16<sup>th</sup> Annual PDF Solutions Users Conference

## PDF/SOLUTIONS"

## S1.4 – DFI<sup>™</sup> and other New Sources of Data for Yield, Reliability and Process Control October 15, 2019 Dennis Ciplickas, VP of Characterization Solutions

This presentation contains forward-looking statements regarding PDF Solutions' future products and business prospects that involve risk and uncertainty. Actual results could differ materially from those discussed. You should review PDF Solutions' SEC filings, including its annual report on Form 10-K and quarterly reports on Form 10-Q, for more information on these risks and uncertainties. PDF Solutions does not undertake an obligation to update any such statements.

© 2019 PDF Solutions, Inc. All rights reserved.

## Introduction

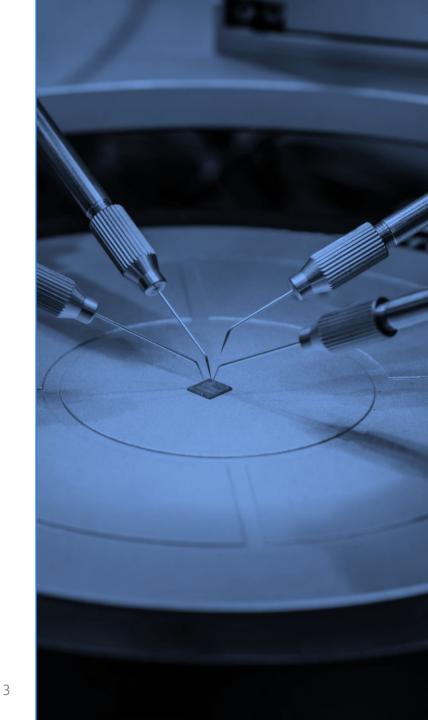

o PDF's business has always been based on data

Deep insight from the unique data generated by our Characterization Vehicle<sup>®</sup> (CV<sup>®</sup>) Infrastructure is a key enabler for time-to-market in our Integrated Yield Ramp (IYR) business

As PDF's analytics business has grown, so has the complexity of semiconductor systems, and the need for unique data persists

We are extending, re-inventing and re-deploying IYR technology to create synergy with Exensio<sup>®</sup> analytics and new offerings for the evolving semiconductor ecosystem

## **Industry Trends**

- o Automotive

- Advanced Driver-Assistance Systems (ADAS)

- Aggressive move into advanced technology nodes

- Functional Safety

- Quality

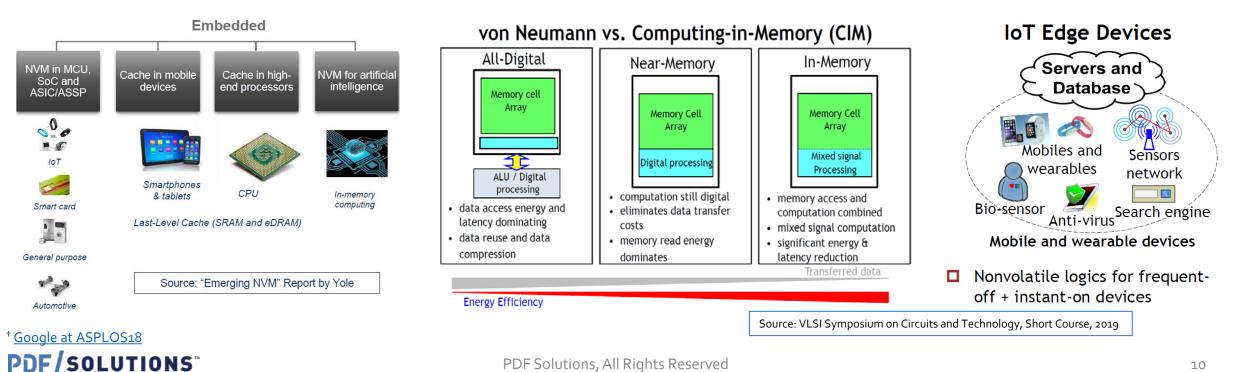

#### o Data center

- New computing architectures

- CPU, GPU, AI, in-memory computing

- New memory and storage architectures

- SRAM, NVM, DRAM, NAND FLASH, HDD

- Power consumption, Power vs. Performance vs. Reliability tradeoffs

- Uptime, SLAs

#### $\circ$ Mobile

- Small, dense form factors with advanced packaging

- InFO, CoWoS, FOWLP, EMIB, etc.

- 5G networking creates technology platform with need for more storage

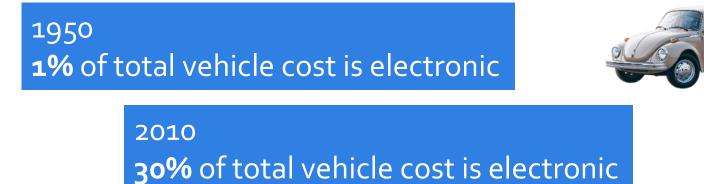

## **Quality Driver: Automotive Electronics**

Est. 2030<sup>†</sup> **50%** of total vehicle cost is electronic

| 5,000                     | <b>1ppm</b> fa |

|---------------------------|----------------|

| semiconductor devices per | rate = 5 fail  |

| average car               | 1,000 cars     |

**1ppm** failure rate = 5 failures every 1,000 cars

10,000 cars manufactured per day

= 2 failures each hour!

## Key industries moving to ppb quality levels!

† <u>statista.com</u>

## Power and Performance vs. Reliability

Data Centers consume 3% of total electricity TODAY! †

- Facebook: 100MW data center with 442,368 servers<sup>++</sup>

- Facebook: average server utilization ~40% (265,420 unused servers) ++

- AI: Rat brain 518,400 processors, human brain 1000x more performance needed <sup>+†</sup>

- Poor Reliability leads to Silent Data Corruption, unacceptable latency and lost revenue

o New technology is needed to...

- ightarrow ...achieve 10x lower power to continue growth

- ightarrow ...enable reliability that meets aggressive SLA commitments

\* forbes.com \*\* FLASH Memory Summit 2018 PDF/SOLUTIONS\*

## Memory Driver: Data Volume + New Computing Architectures

| Flash Storage <ul> <li>3D NAND</li> <li>Cost/Bit scaling</li> <li>Channel Hole Density</li> <li>Vertical Scaling</li> <li>Bits/Cell Increase</li> </ul> | <ul> <li>Persistent memories</li> <li>X-Point Memories</li> <li>Power/Speed scaling</li> <li>Cost/Bit scaling</li> <li>Min X-Y dimensions scaling</li> <li>Multi-layer 3D-stacking</li> </ul> | <ul> <li>In-Memory Compute</li> <li>Low-Power, Low-Latency<br/>embedded NVM</li> <li>Multi-level, Analog<br/>Programming</li> <li>Power/speed scaling</li> <li>Cost reduction</li> </ul> | <ul> <li>Embedded Memories</li> <li>Low-Power, Low-Cost<br/>code, data storage for<br/>microcontrollers, IoT</li> <li>Cost reduction</li> <li>Reliability improvement</li> <li>Power reduction</li> </ul> |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>NEEDS:</li> <li>Fast Node transition</li> <li>High Yield</li> <li>Innovation</li> </ul>                                                        | <ul> <li>3D-stacking</li> <li>Fast Node transition</li> <li>High Yield</li> </ul>                                                                                                             | <ul> <li>Fast development and<br/>co-integration with Logic</li> <li>Performance/Yield</li> <li>Cost reduction</li> </ul>                                                                | <ul> <li>Fast development and<br/>co-integration with Logic</li> <li>Reliability/Yield</li> <li>Cost reduction</li> </ul>                                                                                 |

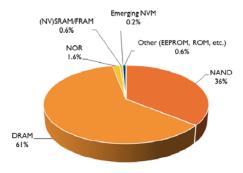

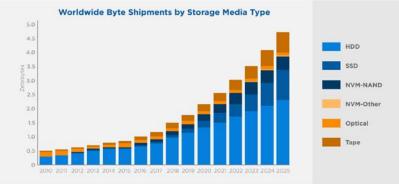

#### 2018 Memory Market - Breakdown by Technology

#### Figure 10 - Worldwide Byte Shipments by Storage Media Type

ource: Data Age 2025, sponsored by Seagate with data from IDC Global DataSphere, Nov 2018

Total Stand-Alone Market in 2018 ≈ \$165 billions Source: Yole, MRAM Developer Day, Flash Memory Summit 2019

PDF Solutions, All Rights Reserved

## **Key Takeaways**

Reliability

Safety, quality, and uptime are of paramount importance for new systems

New chip technologies demand new sources of data to ensure reliability

"Yesterday's yield problem is tomorrow's reliability problem"

Rapid learning cycles are essential to creating a quality product

Massive data collection is necessary to properly characterize reliability

Quick, efficient data collection maximizes impact

#### Foresight

Closing the loop "from fab to field" enables predictive models

New, optimized and efficient operational flows are made possible with AI

## PDF Differentiated Data for Reliability, Efficiency, and Foresight

## **Emerging Memories**

$\circ$  62.7% of the total system energy is spent on Data movement<sup>+</sup>  $\rightarrow$  In-Memory Computing  $\circ$  Low latency Low-Power memory replacement SRAM  $\rightarrow$  MRAM for L<sub>3</sub> Cache?  $\circ$  Emerging memories for Deep Learning  $\rightarrow$  On-chip High Density, Low Power solutions needed  $\circ$  Embedded memories for Automotive and IoT at 28nm and below  $\rightarrow$  Low power, High Reliability

## **Enabling Emerging Memory Development**

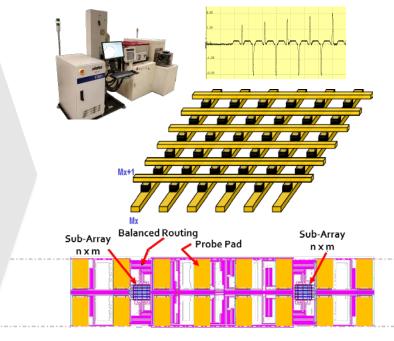

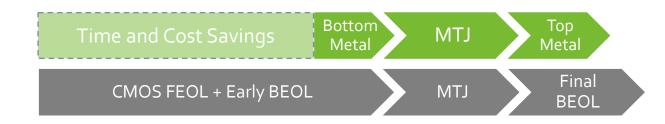

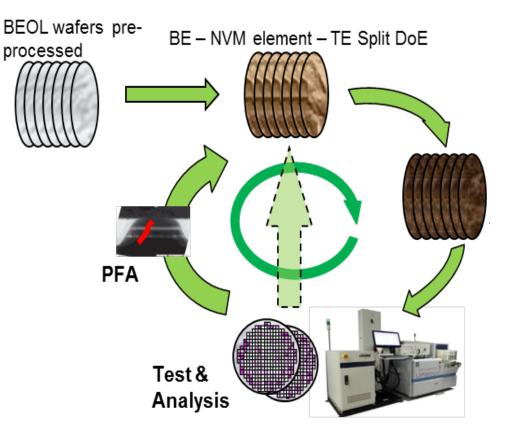

Full flow lots fabricate both back-end memory element and front-end selector devices  $\rightarrow$  slow

Cross-point array with pdFasTest<sup>®</sup> parallel parametric pulse testing enables *efficient* learning

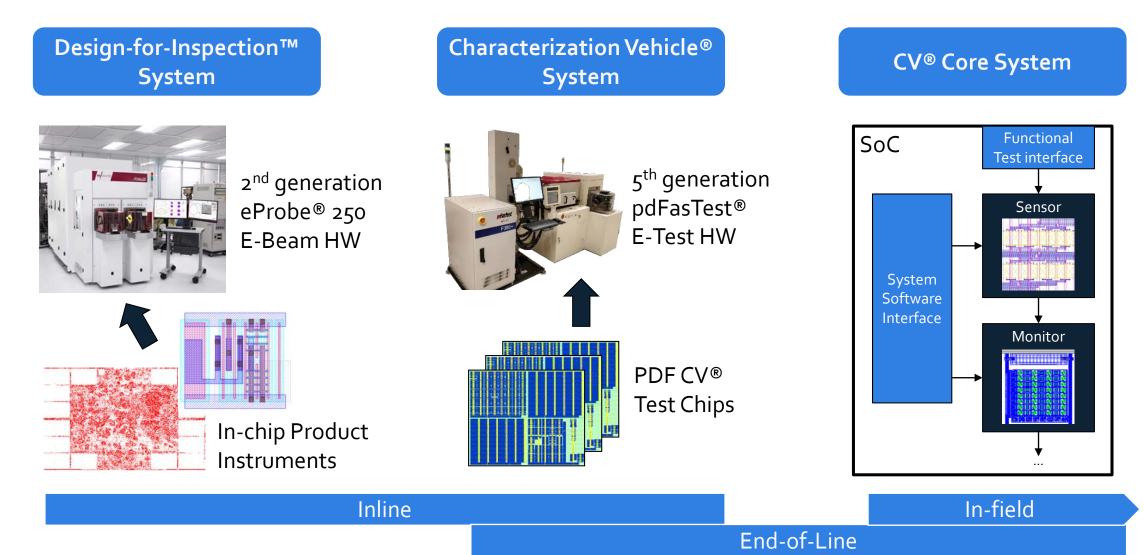

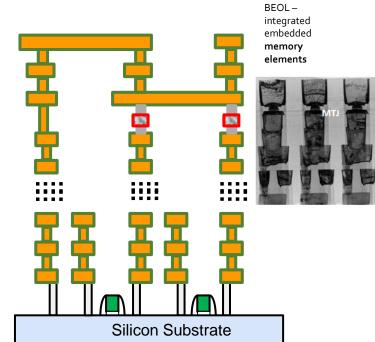

#### **PDF Characterization System for Emerging Embedded Memories**

- Unique Platform for BEOL-integrated Emerging Memories → MRAM, PCM, ReRAM

- Innovative test structure and test method

- Cross Point Array for high Bit statistics

- pdFasTest® F380+ highly parallel pulsed parametric test

- o Characterize millions of bits, millions of cycles in just hours

PDF's fast-learning characterization system *efficiently* enables the promise of emerging BEOL-embedded memories

## PDF Differentiated Data for Reliability, Efficiency, and Foresight

**PDF**/SOLUTIONS<sup>\*</sup>

Inputs from our Partners

○ "Detect the Undetectable" → Find electrically relevant defects buried inside 3D structures

"We are not late on a program because of functional yield, what kills us is we give the customer a chip, they package it, burn it in and figure out that there is a fundamental issue in a material stack or layout configuration. When that happens we lose 6 months to a year."

"We need a non-contacting in-line solution for every wafer"

o "Can you measure every die in-line and predict reliability?" → Reliability Grading

## The Advantages of the DFI<sup>™</sup> System

DFI Capability

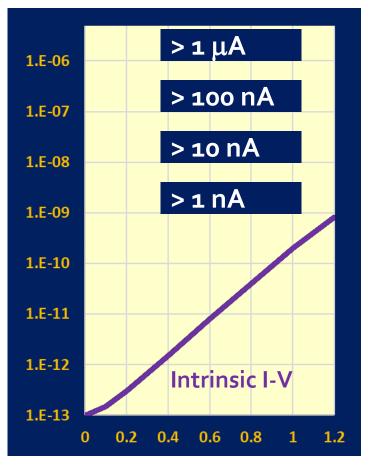

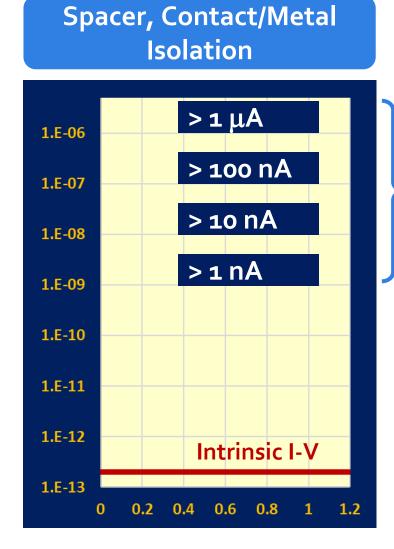

O DFI is a contactless electrical test measurement using an e-beam system

O DFI measurement speed (raw): 100M's DUTs/hr today, Billions of DUTs/hr next

O Calibrated Leakage Value: pA to nA baseline, capture outliers >10x

## DFI Fill Cell

o DFI DUT quantity:

o In-die Reliability monitor:

o Reliability grading:

1B to 100B/wafer using in-product DFI fill cells Focused DUT Design with DOE variants Wafer and Die-level

#### **DFI Scribe**

o DFI measurement density:o Yield metrology:

10-20M DUT's/mm2 (product-like environment) Misalignment, Process window, Root-cause Detection, Hot-spot/Defect monitor

## Why Does Leakage Matter?

Gate Dielectric

It is incredibly difficult to catch such tiny leakages in 10B's of transistors per chip

> Leakage Outlier Bins Identify Latent TDDB Weak Spots RELIABILITY RISK

> > Typical Causes:

• Pinholes

- Dimensional Variation

- Process Damage

- Mechanical Stress

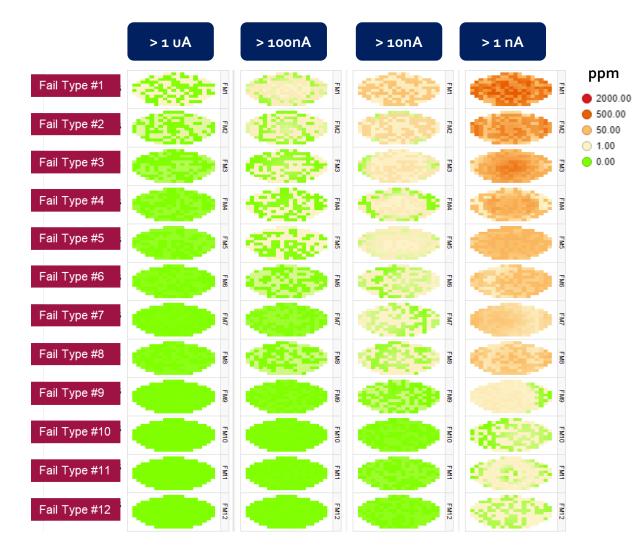

## **DFI™ Data: DUT Leakage Failure Rate Statistics**

- Green die are zero ppm: Die with no failures observed

- Leakage level provides unique reliability insight into latent weak spots

- A composite of different fail mode estimates can indicate risk for early die failure or long term reliability

DFI *efficiently* scans billions of structures per wafer and catches tiny leakages at ppm to ppb levels, providing *early visibility* into potential *reliability risks*

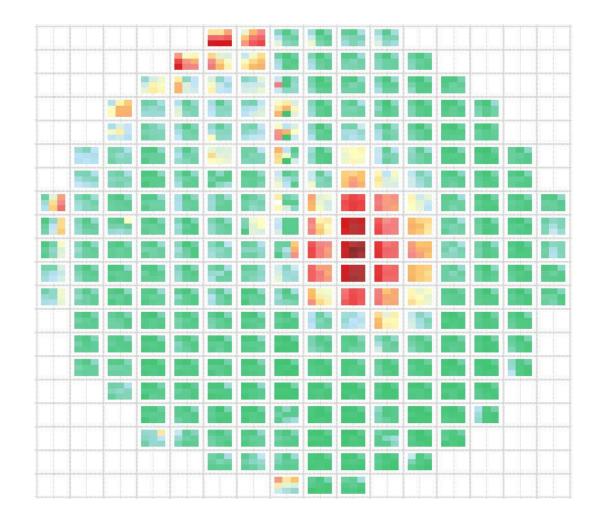

## **DFI™** Die Control: Risk Grading

- High resolution map of every die for single fail type or composite of all fail types

- Spatial signature determines good/bad/risky die

- Within die perspective to assess risk for across field variability or local risk to certain fail type

Detailed across-die measurement creates foresight and enables better risk screening per die than gross methods such as GDBN ("Good Die Bad Neighborhood")

#### **PDF/SOLUTIONS**<sup>\*</sup>

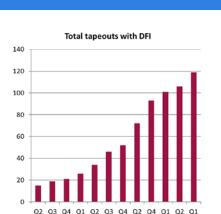

### What is DFI<sup>™</sup> status today?

#### eProbe<sup>®</sup> System

- o eProbe® 150: Running in full automation in 3 R&D fabs

- o eProbe<sup>®</sup> 250: 1<sup>st</sup> tool running in full automation in production fab

15 15 15 16 16 16 16 17 17 19 19

Silicon

- Over 100 tape-outs to date, spanning 6 nodes

- ~6• Product/MPW tape-outs with DFI content

## DFI<sup>™</sup> Accomplishments 2019

#### eProbe® 150

eProbe® 150 and Exensio DFI deployed at multiple sites using dense DFI test chips with throughput 10M's cells/hr

• In active use for yield learning on multiple nodes (22nm, 14nm, 7nm, 5nm)

#### eProbe® 250

Demonstrated fill cell measurement throughput at 500M Cells/Hr

Achieved first install in production fab complete with full automation

Deployed for both scribe app and filler cell app at 7nm, 5nm in progress

Demonstrated calibrated contactless leakage monitoring at DUT level

Demonstrated applications for 3D NAND

#### **PDF/SOLUTIONS**<sup>\*</sup>

20

## **Plenty of Work Remains!**

- Demonstrate production-worthy wafer level and die-level reliability grading app by leakage monitoring of critical fail modes

- O Make DFI<sup>™</sup> an essential element for fab control by providing insight into otherwise undetectable issues

- O Expand applications of DFI<sup>™</sup> into 3D NAND & other non-logic technology

## PDF Differentiated Data for Reliability, Efficiency, and Foresight

#### **PDF/SOLUTIONS**<sup>\*</sup>

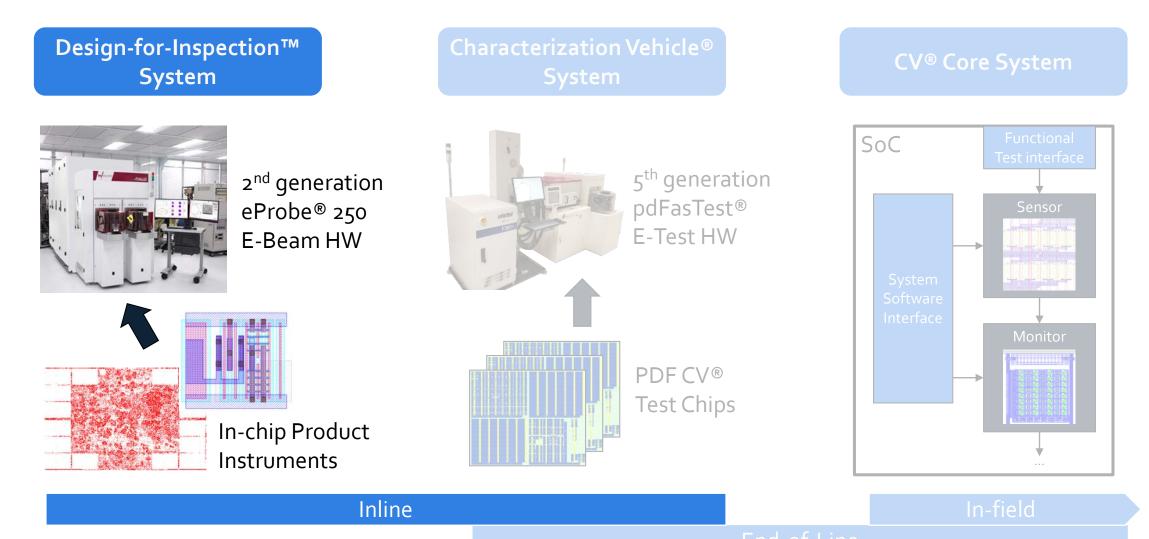

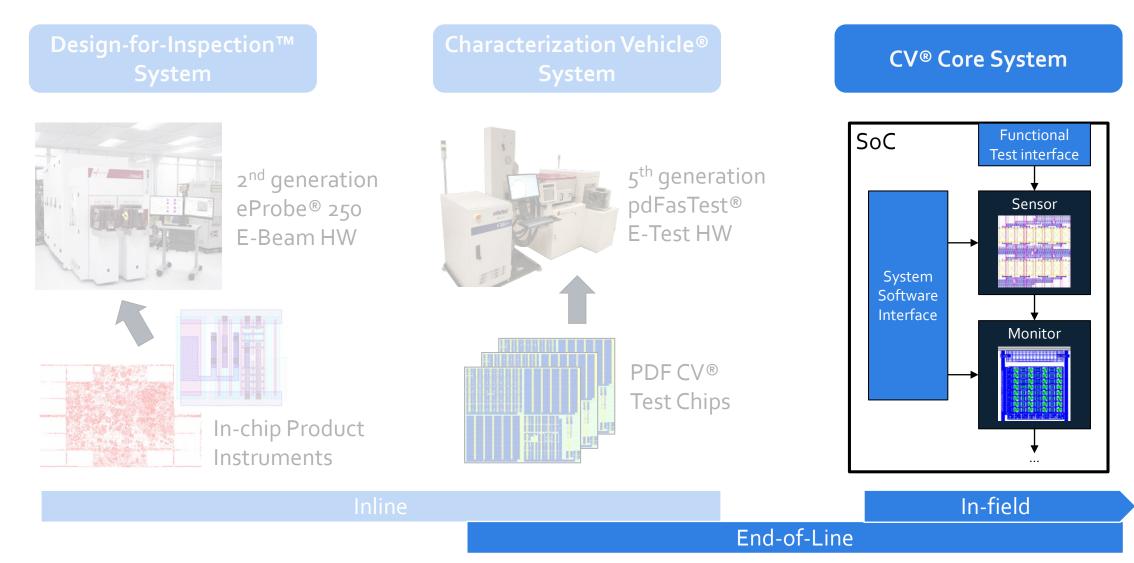

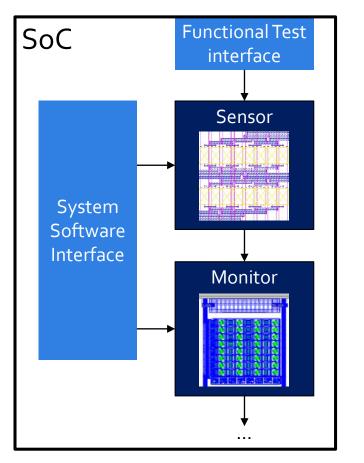

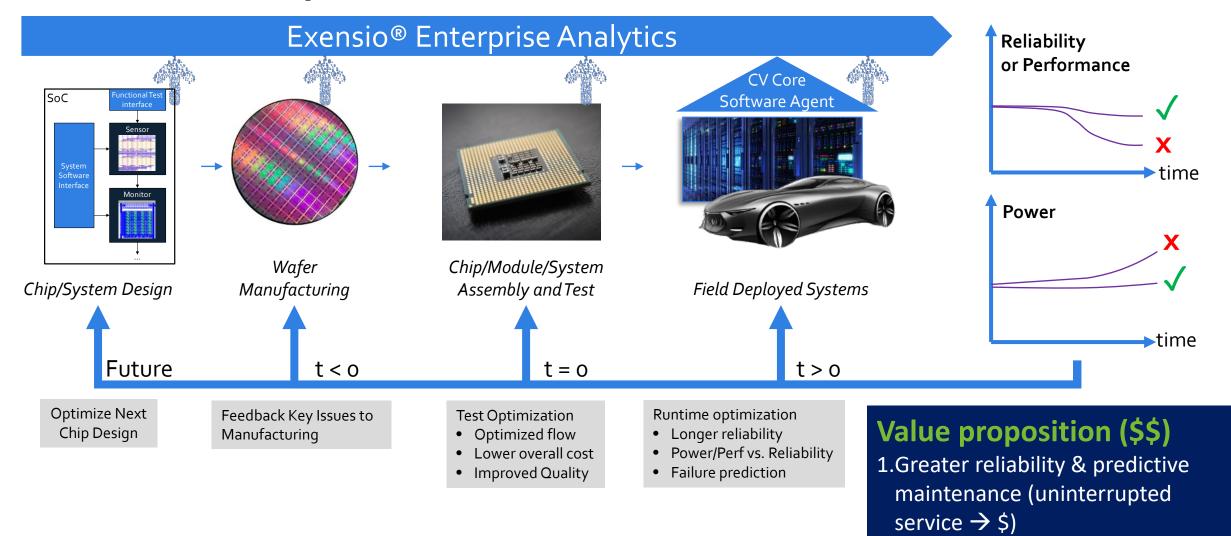

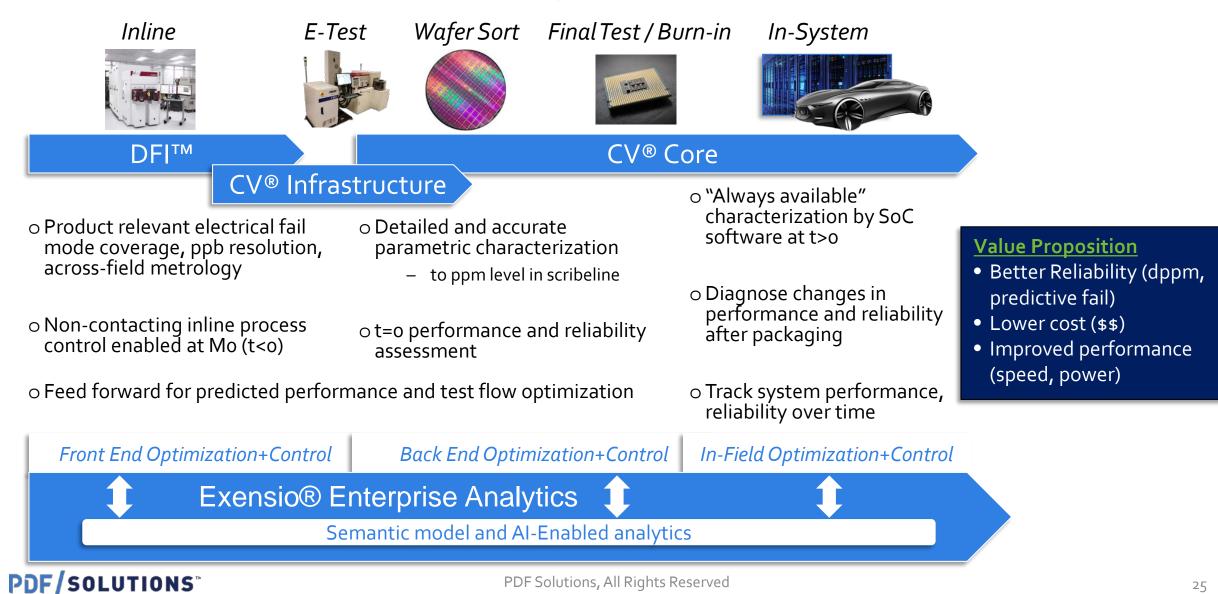

## Leveraging IYR Technology: The CV<sup>®</sup> Core System

- The CV Core System integrates into your performance and reliability optimization strategy:

- Capture weak die at t=o

- Monitor Degradation in the field

- Detect Change/Failure, Self Diagnosis, Failure Prediction

- $\,\circ\,$  PDF CV Core IP blocks are integrated using standard IP flows

- GDS hard macro, LVS netlist, Verilog functional model, I/O spec

- $\,\circ\,$  The CV Core System enables:

- Efficient t=o reliability and performance screening

- Mission mode t>o reliability, performance monitoring, optimization

- Seamless chip genealogy "From Fab to Field" for chip performance and reliability optimization across the complete product lifecycle

### The CV<sup>®</sup> Core System

#### **PDF**/SOLUTIONS<sup>\*</sup>

2.Product optimization (MWh  $\rightarrow$  \$)

#### PDF Differentiated Data Leverages Exensio<sup>®</sup> End-to-end Analytics

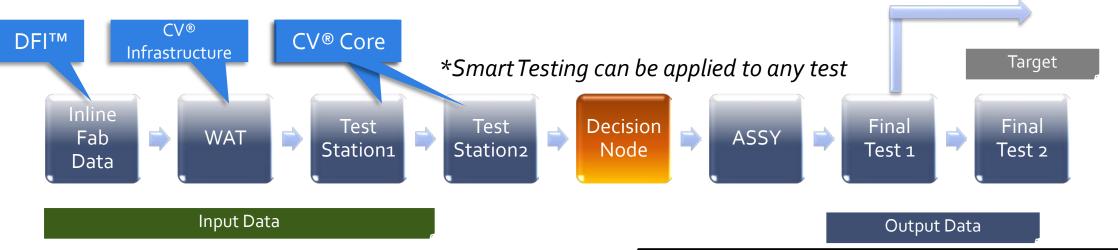

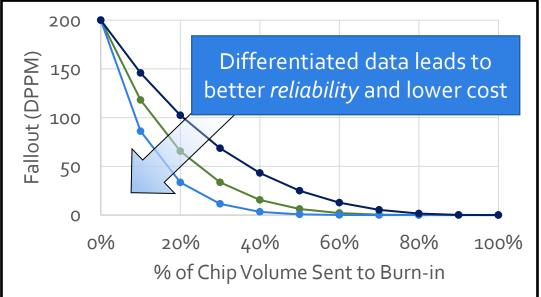

## Smart Testing -> Benefits from Differentiated Data

#### <u>Goals:</u>

- o No risky chips to field, while diverting chips from expensive tests

- Improve quality and reliability by quickly identifying the root cause of field returns

- Focus test resources on product that are at the highest risk for failure

- Reduce test cost by diverting low-risk product volume away from expensive tests

- o Smarter product binning by quality

### Summary

- o PDF's business has always been based on data

- o Semiconductor system complexity continues to increase

- We continue to innovate new sources of data to efficiently improve reliability, performance, and yield, and reduce cost

- The Exensio<sup>®</sup> end-to-end analytics platform leverages this data to create *foresight* and optimize operational flows

# Than Alou

## PDF/SOLUTIONS"

0

pdf-solutions pdfsolutionsinc

pdfs.inc pdf\_solutions

pdf\_cn