## PDF/SOLUTIONS

2024 PDF Users Conference - China

**Parkyard Hotel Shanghai** – 669 Bibo Road, Shanghai, China, 201203

## **Automotive Solutions**

Marc Jacobs – Sr Dir Solutions Architecture, R&D 15<sup>th</sup> March 2024 This presentation and discussions resulting from it may include future product features or fixes, or the expected timing of future releases. This information is intended only to highlight areas of possible future development and current prioritizations. Nothing in this presentation or the discussions stemming from it are a commitment to any future release, new product features or fixes, or the timing of any releases. Actual future releases may or may not include these product features or fixes, and changes to any roadmap or timeline are at the sole discretion of PDF Solutions, Inc. and may be made without any requirement for updating. For information on current prioritizations and intended future features or fixes, contact sales@pdf.com.

PDF Solutions, Exensio, CV, Cimetrix, the PDF Solutions logo, and the Cimetrix logo are registered trademarks of PDF Solutions, Inc. or its subsidiaries. All other trademarks cited in this document are the property of their respective owners. Exensio visualizations Powered by TIBCO<sup>®</sup>.

© 2024 PDF Solutions, Inc. or its subsidiaries. All rights reserved.

## **Automotive Market is growing fast**

#### Increasing semiconductor percentage in cars

| End vertical    | Example                                | % of total<br>2020 | % of total<br>2025E | 2025 revenue<br>projection | 2021E-<br>2025E%<br>CAGR |

|-----------------|----------------------------------------|--------------------|---------------------|----------------------------|--------------------------|

| Automotive      | ADAS,<br>Infotainment<br>Chassis       | 8.3%               | 12.0%               | \$80.28                    | 12.4%                    |

| Communication   | Smartphones                            | 32.9%              | 31.5%               | \$210.3B                   | 3.0%                     |

| Consumer        | TVs, Digital<br>Set-Top Box            | 10.4%              | 10.5%               | \$70.3B                    | 2.6%                     |

| Data processing | PCs, Servers,<br>Storage Media         | 37.7%              | 33.8%               | \$225.6B                   | 1.6%                     |

| Industrial      | Automation,<br>Healthcare,<br>Security | 10.7%              | 12.1%               | \$80.7B                    | 8.5%                     |

Exhibit 24: Semiconductor worldwide revenue by end vertical, sales (source: Gartner)

#### Overall Automotive 2025: 80B USD, 12.4% CAGR

Source: Accenture

**PDF**/SOLUTIONS<sup>T</sup>

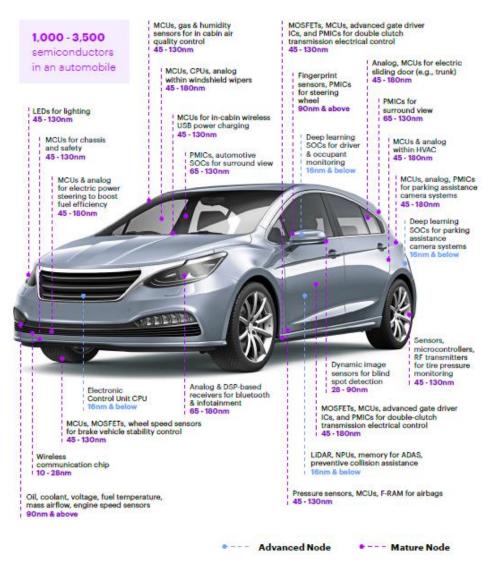

#### Exhibit 34: Subset of advanced & mature nodes in an automobile

#### © 2024 PDF Solutions, Inc. or its subsidiaries

3

## New technologies driving Automotive Market

**EVs**

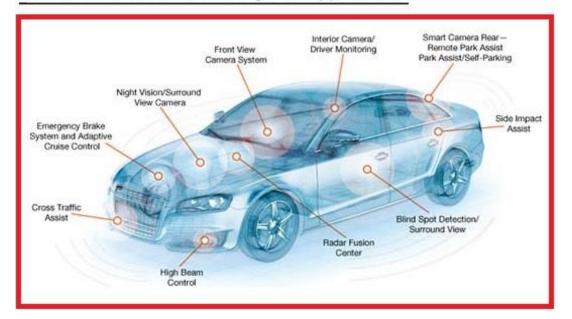

#### Advanced Driver Assistance System Applications

Advanced Driver Assistance System Applications ~ NEW TECH (mytech2u.blogspot.com)

ADAS

Increased semiconductor percentage and complexity of the car

## **PDF Can Help You Succeed**

- Solutions for Fabless

- Solutions for Foundries and IDMs

- Specialized solutions for Silicon Carbide

- Software

- Equipment

- Test Structures,

- & Methodologies

## **Health Check**

## **Health Check: Basic and Advanced**

## What do we mean by basic & advanced?

- Basic = mature technologies

- Planar transistors ~22nm & above

- Single die packages

- Advanced = newer technologies

- 16nm FINFET & beyond

- Multi-chip packages

### Note: "Basic" in automotive does not mean *easy*

## **Health Check Results: Overall**

|           | New Entrants |          | Incum | pents    | Best in Class Incumbents |          |  |

|-----------|--------------|----------|-------|----------|--------------------------|----------|--|

| Category  | Basic        | Advanced | Basic | Advanced | Basic                    | Advanced |  |

| Design    | 69%          | 44%      | 86%   | 52%      | 95%                      | 75%      |  |

| Fab Mfg   | 59%          | 40%      | 92%   | 76%      | 100%                     | 100%     |  |

| Packaging | 74%          | 65%      | 94%   | 88%      | 95%                      | 100%     |  |

| Test      | 71%          | 55%      | 74%   | 54%      | 95%                      | 83%      |  |

#### Areas for Improvement – New Entrants

- Fault Coverage (!)

- Pick the right Foundry if you are fabless

- Regular layout

- FDC with BIC control plans

- Characterization Vehicles (CVs) for DFM

- Margin WAT

#### Areas for Improvement – Achieving Best-in-Class

- Quality Shield

- Adoption of traceability

- Fault localization

## **Solutions for Silicon Devices**

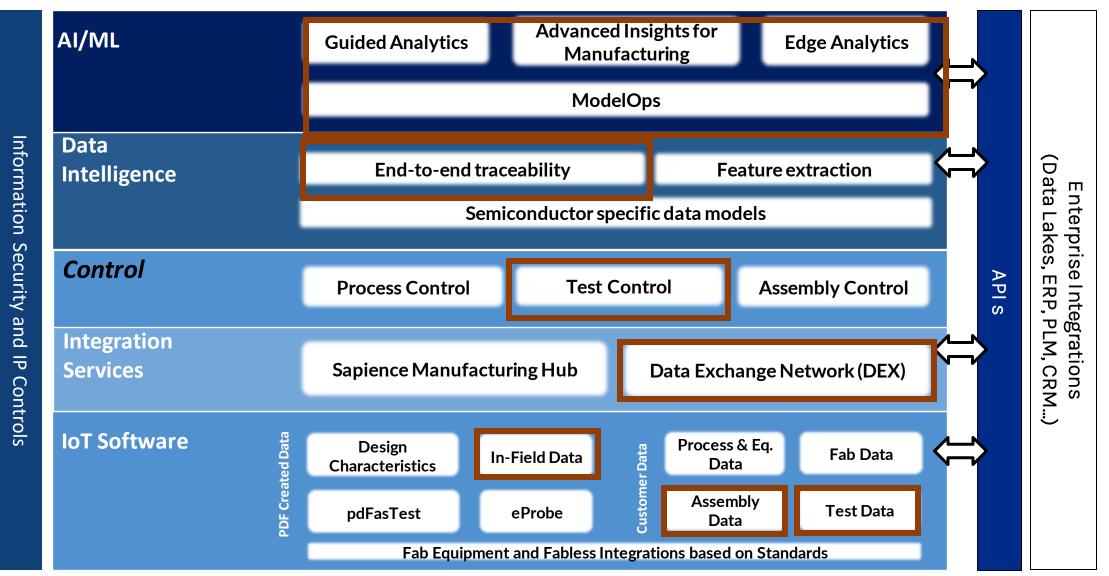

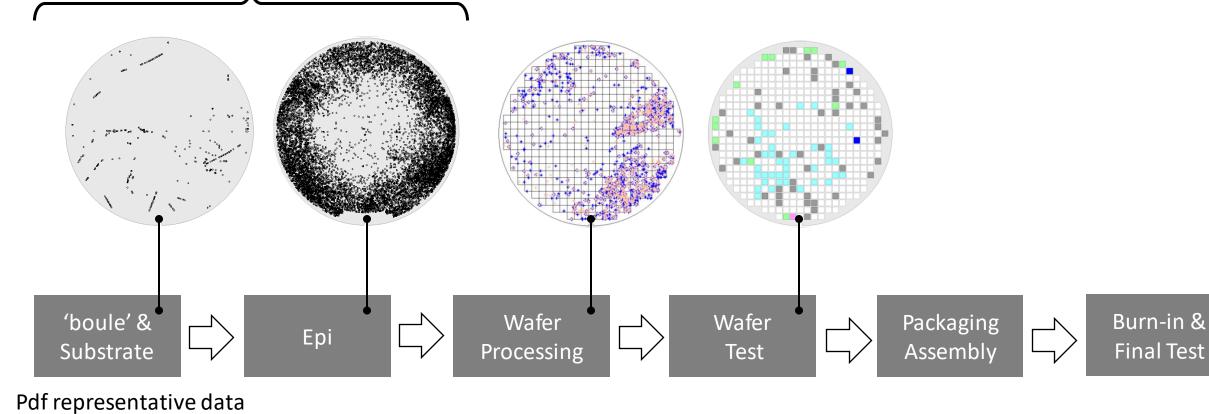

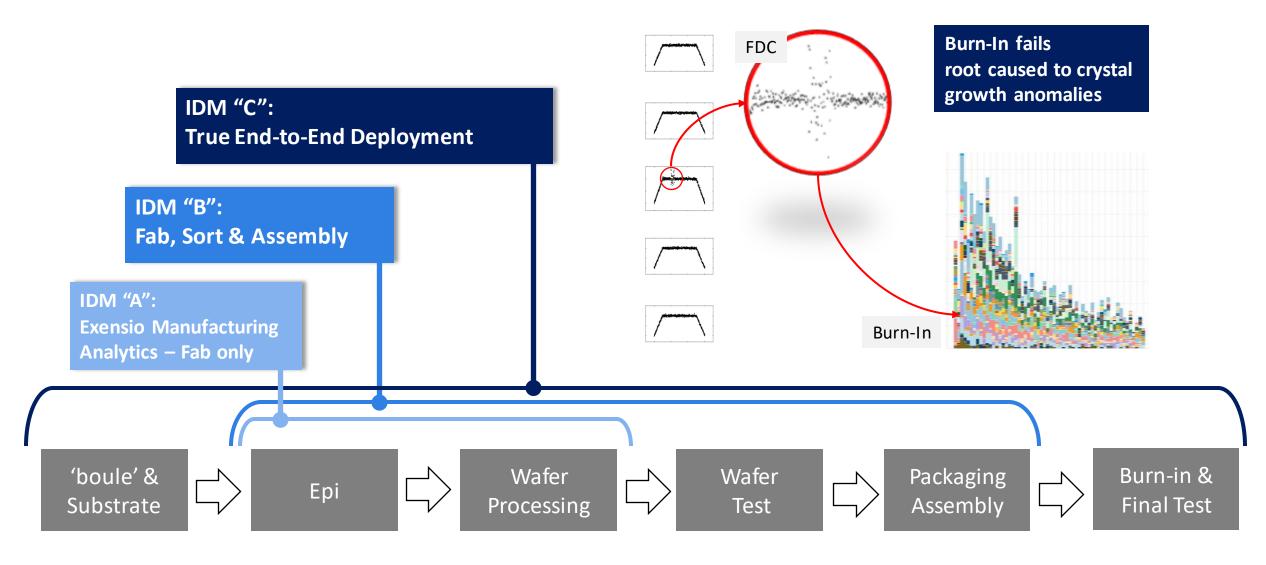

## **End-to-end Integrated Platform for Semiconductor Analytics**

## Silicon Product Lifecycle

| Process<br>Development | <ul> <li>Regular Layout</li> <li>Characterization Vehicles</li> </ul>                                |

|------------------------|------------------------------------------------------------------------------------------------------|

| NPI/Char               | Characterization                                                                                     |

| Yield Ramp             | <ul> <li>Accelerating Yield Analysis</li> <li>Machine Learning for Optimized Test</li> </ul>         |

| HVM                    | <ul> <li>Best-in-Class Operations at Test</li> <li>Supply Chain Visibility &amp; Security</li> </ul> |

| In-Field               | Failure Analysis & Returns                                                                           |

## **Process Development Phase**

## Make the Process Right EARLY

#### Build on a solid foundation

- **Fix the problems early in the process**

- Don't wait for Test and hope to screen

- Test will miss things

#### Early means both

- Early in the development cycle

- -And

- Early in the process flow

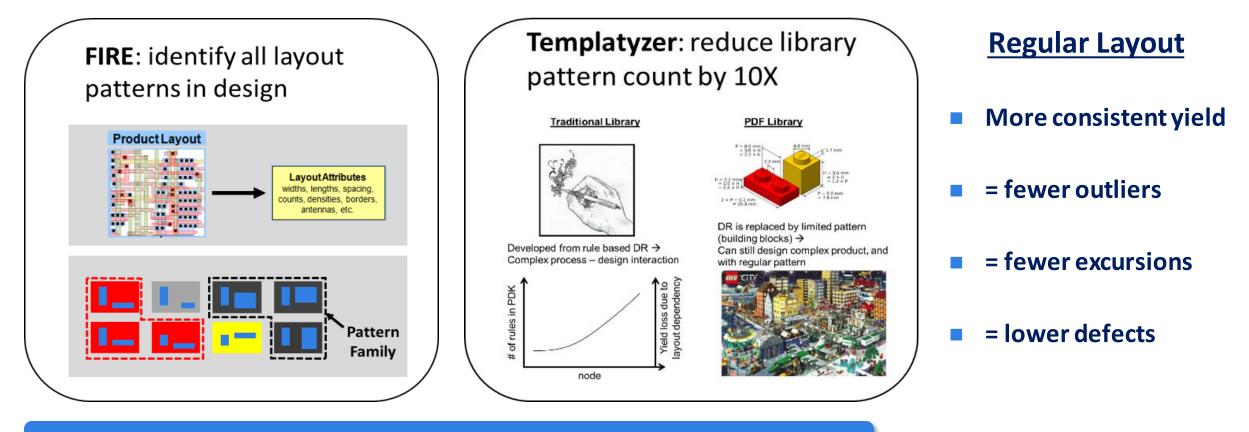

## Be the right fab / Pick the right fab

- What the customer wants

- Superior yield

- Excellent process control

- Fewer excursions

#### How to get it

- Regular layout

- Characterization Vehicles (CVs) for DFM

- Margin WAT

- **FDC with BIC control plans**

For Foundry & IDM Be the right fab

**PDF/SOLUTIONS**<sup>\*\*</sup>

#### How to get it

- Pick the right foundry

- One that uses these methodologies

#### For Fabless Pick the right fab

## **Design to Enable Zero Defect**

#### Identify and Reduce Layout dependency

FIRE/Templatyzer for right-first-time

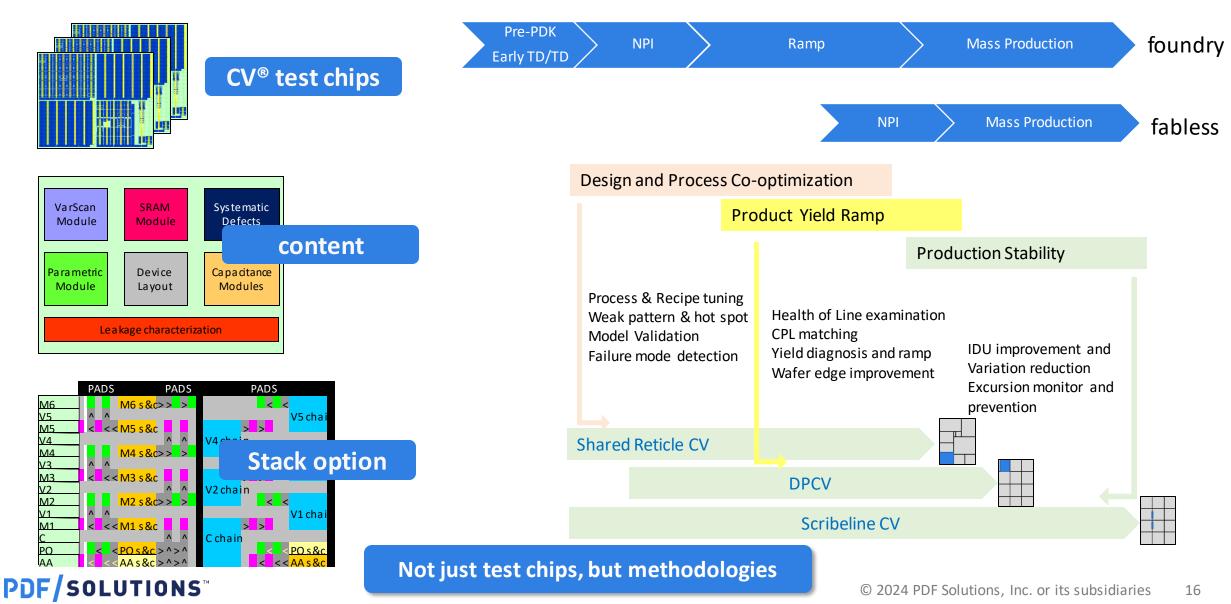

## **Characterization Vehicles & Test Structures**

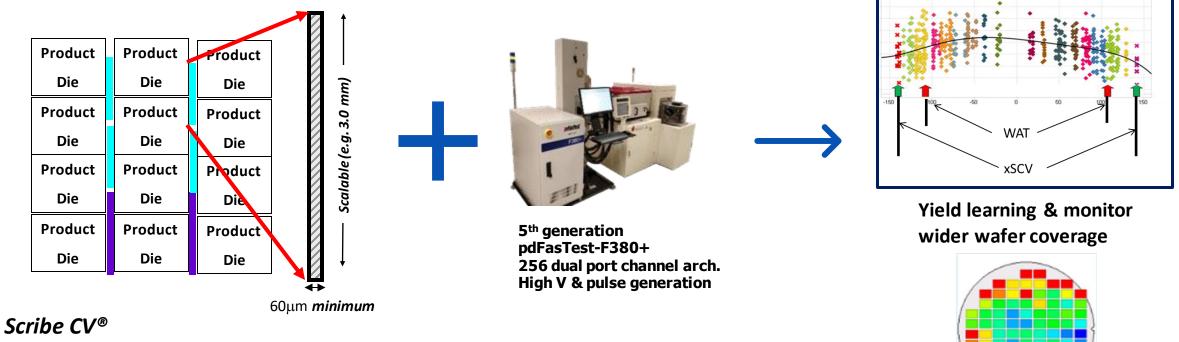

## ScribeCV – PDF's Solution for Margin WAT

Device, Yield, Parametric, Leakage

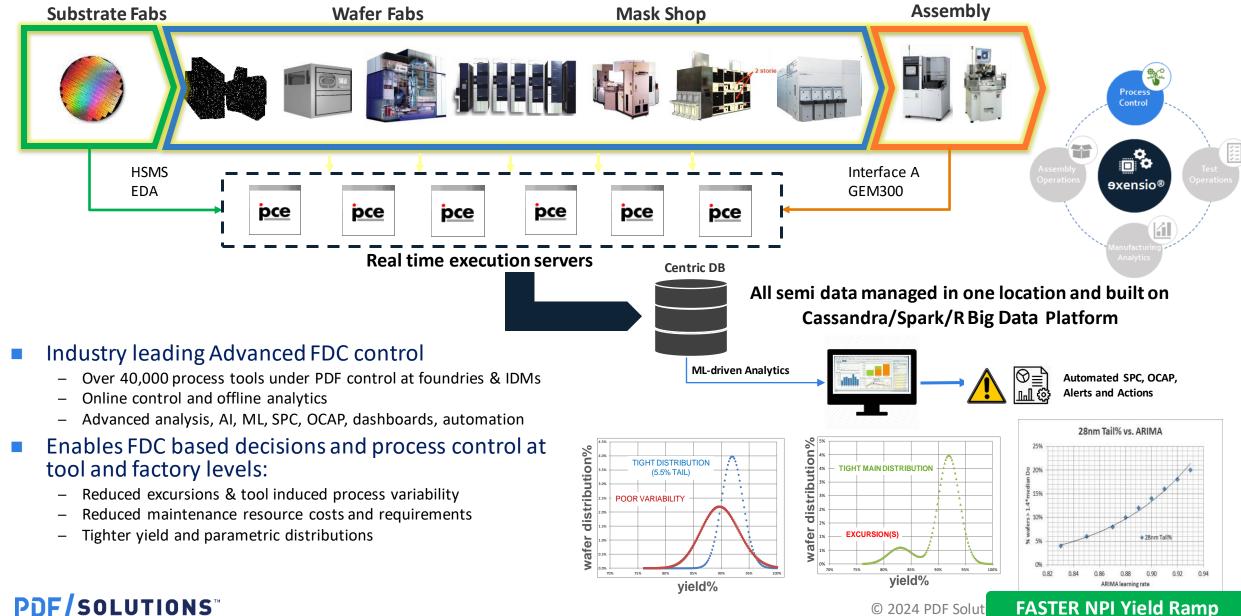

## **Process Control: Advanced FDC for Semi Manufacturing**

#### **PDF**/SOLUTIONS<sup>\*\*</sup>

© 2024 PDF Solut

## **NPI – New Product Introduction**

## **New Product Introduction & Characterization Feature Matrix**

| Capability                                      | Exensio<br>Manufacturing<br>Analytics | Partnership  | Inc. Fail %<br>75.03%<br>7.34%<br>6.79%                         | Cum. Fail %<br>75.03%<br>82.37%<br>89.16% | Cum. Fail Pareto                                                                                                  | 360 -<br>300 -<br>260 -        | Color by:<br>CaleLot<br>■ Comp<br>■ Ref                                                                                |

|-------------------------------------------------|---------------------------------------|--------------|-----------------------------------------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Test Program Validation & Optimization          |                                       |              | 4.64%<br>1.35%                                                  | 93.81%<br>95.16%                          | 1                                                                                                                 | 200 -                          |                                                                                                                        |

| Test Coverage (Never failing / Redundant tests) |                                       |              | 1.35%                                                           | 95.16%                                    |                                                                                                                   | 150 -                          |                                                                                                                        |

| Limits Analysis                                 |                                       |              | 0.79%                                                           | 97.10%                                    | 1 1                                                                                                               | 100 -                          |                                                                                                                        |

|                                                 |                                       |              | 0.75%                                                           | 97.86%<br>98.33%                          |                                                                                                                   | 50 -                           |                                                                                                                        |

| Specification, Guard band Limit Setting         | $\checkmark$                          |              | 0.36%                                                           | 98.69%                                    | I I                                                                                                               |                                |                                                                                                                        |

| Product Characterization                        |                                       |              | 0.20%                                                           | 98.89%                                    | I                                                                                                                 | 0.40<br>0.42<br>0.44           | 0.46<br>0.50<br>0.54<br>0.55<br>0.55<br>0.55                                                                           |

|                                                 |                                       |              | 0.16%                                                           | 99.05%<br>99.21%                          |                                                                                                                   |                                | TN_20X20 (20 bins)                                                                                                     |

| Wide / Sweep Data Handling                      | V                                     |              | I Normal Quanti                                                 |                                           | •I                                                                                                                | I Wafer Map                    |                                                                                                                        |

| CP / CPK Analysis, VDD / Temp Char Analysis     | $\checkmark$                          |              | 3.5                                                             |                                           | Color by:<br>Lot ▼ + ▼                                                                                            | LOT_38.1                       | LOT_38.4                                                                                                               |

| Fab / Supplier Matching & Qualification         | $\checkmark$                          |              | 1.5                                                             |                                           | LOT_181,1<br>LOT_38,1<br>LOT_38,4<br>LOT_38,4                                                                     |                                | Product Map<br>Coto Dr<br>Pri A Avg(ORR)<br>99432e-8 - 105148e-7<br>99432e-1 105148e-7 - 11052e-7                      |

| Reporting / Templates / Release to Production   | $\checkmark$                          |              | -0.5 -                                                          |                                           |                                                                                                                   | 1.21e-7[1]<br>LOT_39.1         | 1.19e-7 [1]<br>LOT_181.1<br>LOT_181.1<br>1.10652e-7 - 1.16167e-7<br>1.16157e-7 - 1.21661e-7<br>1.21661e-7 - 1.27166e-7 |

| Design / Layout Sensitivities to Process        |                                       |              | -2.5 -                                                          |                                           |                                                                                                                   |                                | Defect Map                                                                                                             |

| WS / FT to WAT: Die Level Process Sensitivity   | $\checkmark$                          |              | 9.4E-08                                                         | 1.04E-07<br>19 OF                         | 1.14Ė-07 1.24Ė-07<br>RR                                                                                           | 1.14e-7 [2]                    | 1.13e-7 [1]                                                                                                            |

| On Chip Agents                                  | $\checkmark$                          | $\checkmark$ | Box Plot                                                        |                                           | Temp • + •                                                                                                        | 1 Bar Chart                    | Temp                                                                                                                   |

| Fault Diagnostics                               |                                       | $\checkmark$ | 8.80000<br>8.70000<br>8.60000<br>8.50000<br>8.40000             |                                           | 40c<br>0 c<br>125c<br>255c<br>70c                                                                                 | 3.50000                        |                                                                                                                        |

| Fab/Foundry                                     |                                       |              | 8.30000<br>8.20000<br>8.00000<br>8.00000<br>7.90000<br>8.7.8000 |                                           |                                                                                                                   | (J 2.50000                     |                                                                                                                        |

| Design layout sesnitivities                     | <b>V</b> .                            |              | 7,80000<br>7,70000<br>7,60000<br>7,50000                        | 10c 0c 125c                               | 260 70c Alpha level = 0.05                                                                                        | I.80000<br>1.00000<br>5.00000  |                                                                                                                        |

| Split Lot Analysis                              | $\checkmark$                          |              | Count 11<br>Median 8<br>Outliers                                | 28 52 28<br>05 8.045 8.1<br>3 3 0<br>Temp | 82         80         RestMSE = 0.248           8.05         8.07         sqrt(2)q* = 3.877           2         0 | 0.00000<br>7.50 7.60 7.70 7.80 | 2 750 8.00 8.10 8.20 8.30 8.40 8.50 8.60 8.70 8.80 8.90 9.00                                                           |

## **Yield Ramp**

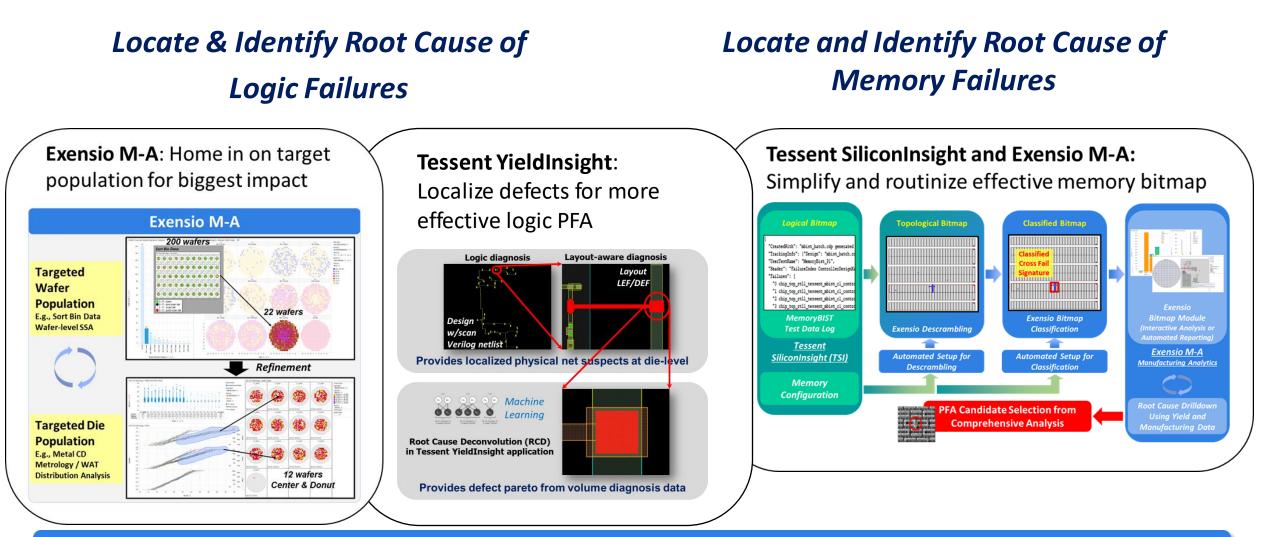

## Yield Ramp & FA Diagnostics: Siemens Tessent + Exensio

Partnership with Tessent for BIC debug and FA

PDF/SULUTIONS

## **HVM – High Volume Manufacturing**

## **Exensio Advanced Quality & Ops Path**

Quality Shield is essential for to compete with Best-in-Class

## **Exensio Advanced Quality & Ops Path**

| <ul> <li>Offline Reporting</li> <li>Floor Monitoring</li> <li>OEE reporting</li> <li>Stoppages / RE<br/>losses</li> </ul> |                                                     | <ul> <li>Real Time Rules</li> <li>Outlier Screens<br/>(DPAT, GDBN)</li> <li>Escape<br/>Prevention (eg<br/>Test count)</li> </ul> |                                                                                                                                  |  |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| <b>Operational Visibility</b>                                                                                             | <b>Operations Shield</b>                            | Quality Shield                                                                                                                   | Machine Learning                                                                                                                 |  |

|                                                                                                                           | Real Time Rules<br>• Site2Site Yield<br>• UPH Limit |                                                                                                                                  | Model Based Prediction<br>Model Based Screening<br>• Predictive Binning<br>• ML Outlier Screening<br>• "Bring Your Own<br>Model" |  |

## **Powerful Rules for OSATs and Fabless**

## **Operations Shield**

#### **Process Control Rules**

- Fab & Packaging Problems

- Test Floor Problems

## **Quality Shield**

#### **Escape Prevention Rules**

Stop errors from shipping

vana

## **Quality Shield**

#### **Outlier Detection Rules**

Catch discrepant units

## Powerful Rules for OSATs and Fabless: Detailed Rule Catalog

#### **Process Control**

- Yield

- Bin Percent / Count

- Lot Begin / End

- Parametric Test Statistic

- Parametric Test Yield

- Site-to-Site

- Yield

- Percent Delta

- Test Statistic Delta

- Parametric Test SPC (WECO)

- Oscillating / Outlier / Trend / Zone

#### PDF/SOLUTIONS

#### **Escape Prevention**

- Consecutive Bin

- Stuck Unit (parametric)

- Test Count

- Bad Device Good Bin

- Good Device Bad Bin

- Limit Fail Good Bin

- Measurement Exception

- Limit Exception

- Device Test Time

- Retest Limit

- Mixed Lot Limit

- Units per Hour Limit

- Valid ECID

#### **Outlier Detection**

- DPAT

- GDBN

- Cluster Detection

- NNR

- Univariate / Multivariate

- Custom rules by equations

WECO Western Electric Co SPC Statistical process Control ECID Electronic/Exclusive Chip ID DPAT Dynamic Part Average Test GDBN Good Die Bad Neighborhood NNR Nearest Neighbor Residual

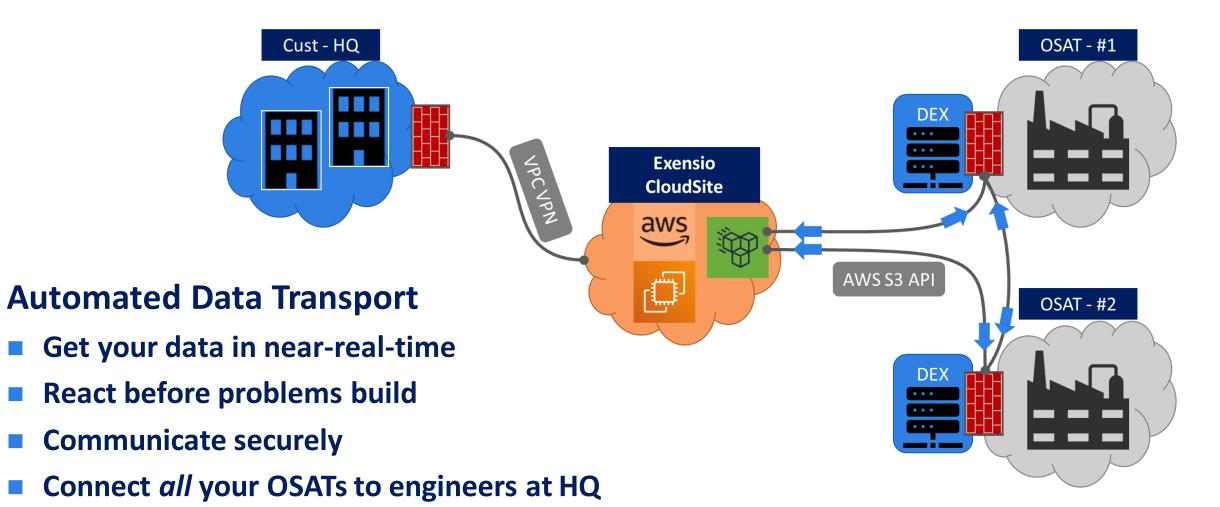

## Data Exchange (DEX) Connects You & Your Suppliers

High-performance managed Exensio deployment with OSAT integration

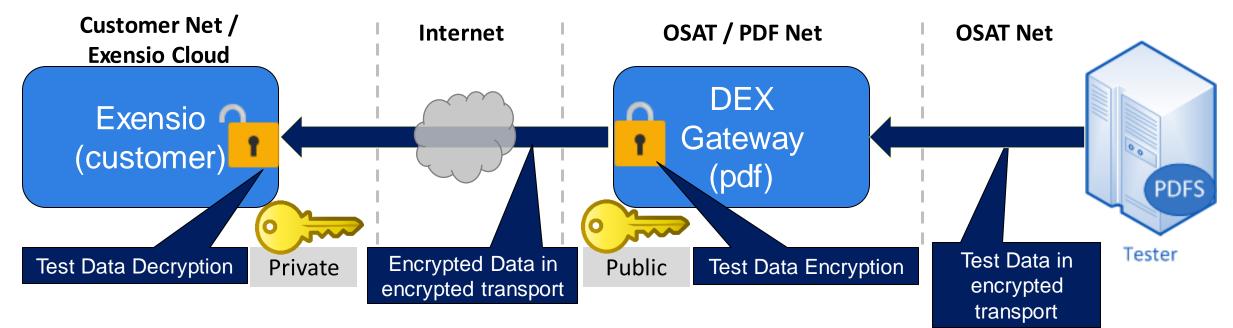

## Security : Encrypted Data Transport (Example: OSAT to Customer)

#### Encrypted Transport Across Public Networks

- Transport between DEX and Exensio nodes is encrypted and private

- Data is transmitted over encrypted tunnel

- Only intended destination server can decrypt transport payloads

- Node-unique private encryption key required to decrypt payloads

- Bulk payload encrypted with AES-256

## **In-Field Failures** Automotive Doesn't End with Device Shipment

## **Containment & Root Cause of Complex FAs**

Despite all your teams' good efforts, you will get FAs (Failure Analysis Requests)

#### Modern products getting more complicated

- Complex supply chains

- Chiplets & 2.5D/3D packages

- Advanced process nodes

- But your customers don't care

- They want the answers, now

#### Traceability & End-to-End Data Analytics make FA easier

## End to End Analytics & Traceability for Better FA/RMA

#### ■ WAT (aka PCM, E-Test)

- Parametric data

#### ■ Wafer Sort (aka EWS, CP)

- Yield, binning

- Wafermaps

- Parametric data

- Equipment Details

#### Final Test (aka Class)

- Yield, binning

- Parametric Data

- Equipment Details

#### Packaging

Substrate Maps

SiPLot1SiP-005

/SiP/Block/Devices/L1D1: 100.00% (2/2) [1]

SiPLot1SiP-008

/SiP/Block/Devices/L1D1: 100.00% (3/3) [1]

# Reconstituted Wafer Maps Use traceability to see failures at each

see failures at each of previous steps

✓ ECID or Exensio

Assembly Ops

#### Defect Localization

- Logic using Scan Fault Diags

- Memory using Bitmap

- Both → Siemens Tessent collaboration

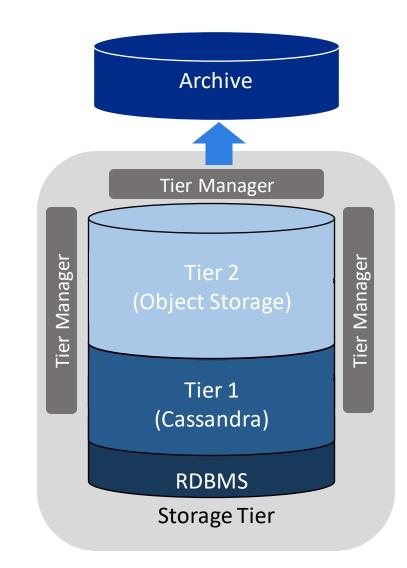

## **Exensio Cloud : Tiered Storage Benefits**

- FA is impossible if you don't keep the data

- Automotive 10+ years data retention

- Keep your new data for fast retrieval

- Keep your old data for when you need it

- Rarely

- But urgently

- Seamless to users / Seamless to integration

## **Solutions for SiC Devices**

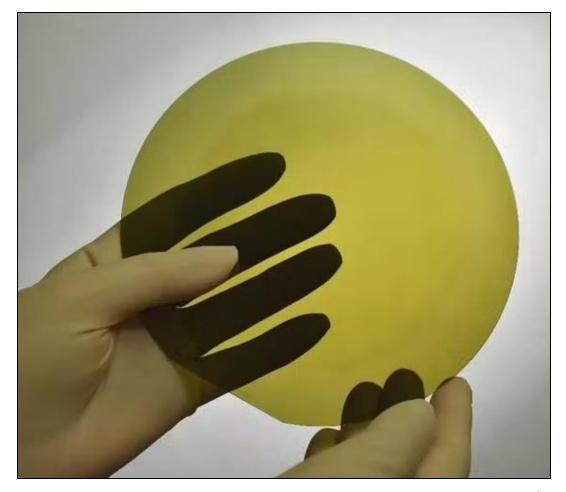

## **Silicon Carbide - Introduction**

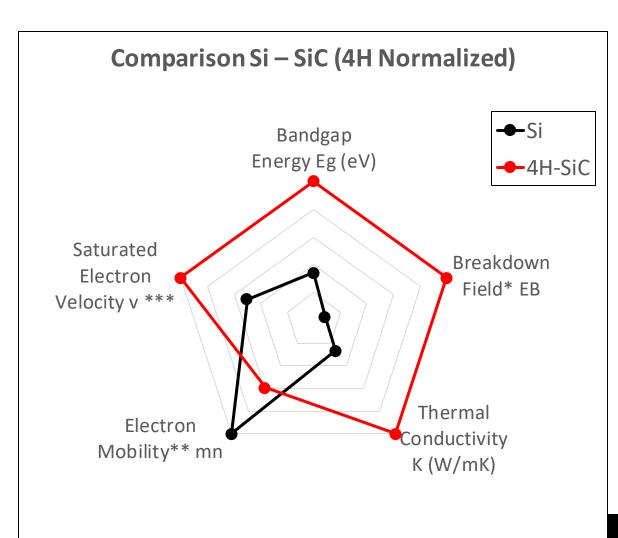

#### Great for Power IC and RF

source: onsemi

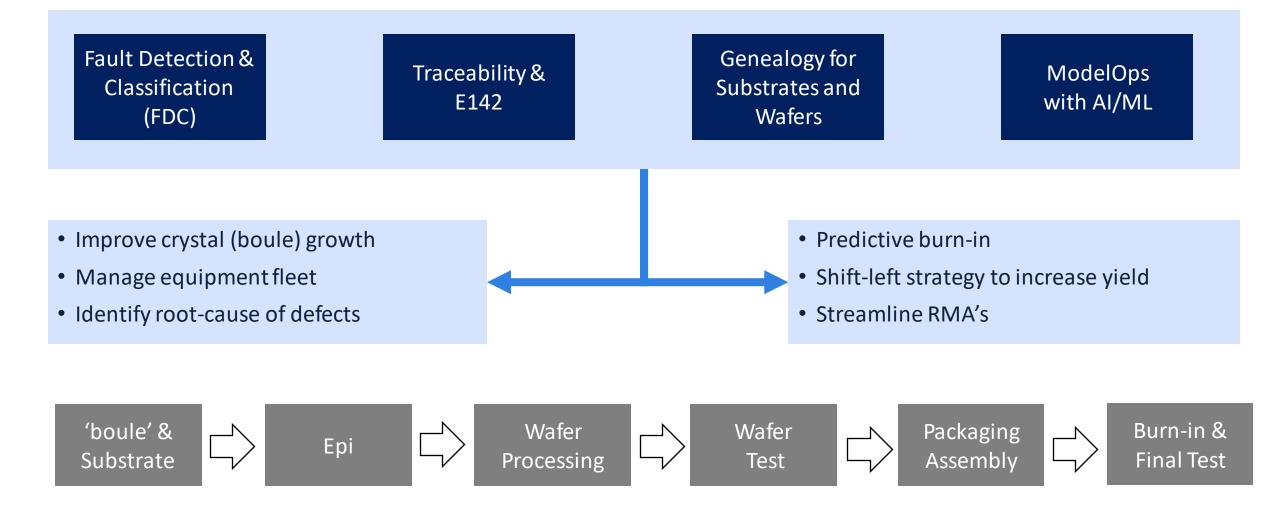

## **Challenges with SiC Manufacturing**

- Complicated (in-house vs outsourced) material flow

- Lot reshuffling: wafer & lot genealogy

- High defectivity

- Equipment connectivity (150 & 200 mm)

- Small pucks vs large boules

- New types of subsurface defects hard to detect with conventional means

- No wafer scribe or ambiguous wafer ID

- Defect sampling for SEM Review: too many

- Unpatterned vs patterned wafers: registration

Compound Semiconductor: stoichiometry matters!

>250 polytypes: stacking faults are common

$\rightarrow$  inquire for more detail

$\rightarrow$  covered in this talk

source: ChemTube3D

## SiC Package for Fabs and IDM's

## **SiC Defectivity**

**PDF**/SOLUTIONS<sup>\*\*</sup>

\$\$\$

#### "SiC is where silicon was decades ago..."

## **Deployment Examples in SiC Manufacturing**

- Electrification & ADAS driving rapid growth

- Many new entrants

- PDF: broadest and deepest analytics solution

- With specialized offerings

- SiC package for EV products

# Thank You

## **PDF**/SOLUTIONS<sup>TM</sup>

pdf-solutions

Ŧ

pdfsolutionsinc

pdfs.inc

pdf\_solutions

pdfs\_cn