# PDF/SOLUTIONS

**Confidential Information**

# SIEMENS

Improve yield by addressing layout pattern systematic defects

**Jayant D'Souza (Siemens)**

# **Agenda**

- Industry trend and problem statements

- Overview of solution

- Silicon results

- Key takeaways

# Acknowledgement

#### **PDFSolutions**:

- Thomas Zanon

- Christian Sendner

- Hans Eisenmann

#### **Siemens:**

- Gaurav Veda

- Randy Klingenberg

- Manish Sharma

# **Industry trend**

- Yield can be impacted by a variety of different factors at all technology nodes

- Random

- Systematic

- Parametric

- Most systematic issues that are the combination of process, design and layout are ironed out early in early ramp and during NPI

- However, in advanced technology nodes, systematic yield issues remain a dominant concern throughout the product lifecycle

- Could impact yield 2-4% points even in HVM

# Problem definition: Identifying layout systematics

- Certain layout patterns can lead to systematic yield loss

- new node, NPI, excursions in volume production

- Such patterns are highly actionable for improving yield

- Leads to root cause identification

- Foundry: process change

- Fabless: design change

- How do we identify these patterns from volume scan diagnosis data?

C. Schuermyer, et.al. (MGC, GF), "Identifying Systematic Critical Features Using Silicon Diagnosis Data", ASMC 2012

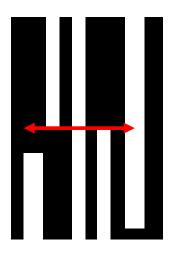

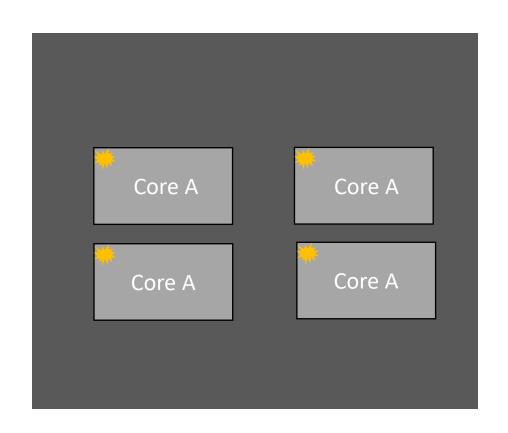

### Repeater sets in Tessent diagnosis data

- A repeater set is a set of identical diagnosis reports (all suspects are the same)

- These are most likely caused by a layout pattern

```

#symptoms=1 #suspects=16 CPU time=9.79sec fail log=OpenPattern 1 wafer1 41 66.flog.gz

#failing patterns=92, #passing patterns=128

#unexplained failing patterns=0

symptom=1 #suspects=16 #explained_patterns=92

64

90

497

suspect score fail match pass mismatch type

value pin pathname cell name net pathname layout status

#potential open segments=3, #total segments=43, #potential bridge aggressors=0, #total neighbors=na

suspect score fail match pass mismatch type

value location layout layer critical area

B13 metal1

1.29E-02

vial

metal2

2.58E-02

via2

3.08E-03

metal3

1.29E-02

1.29E-02

via3

3.08E-03

9.62E-03

metal4

B11&B13&B22 metal3

```

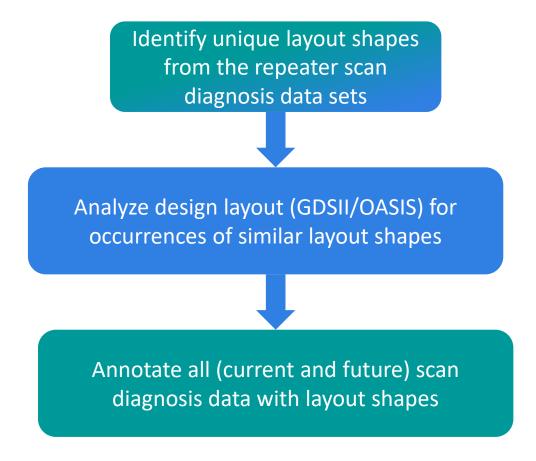

# **Approach**

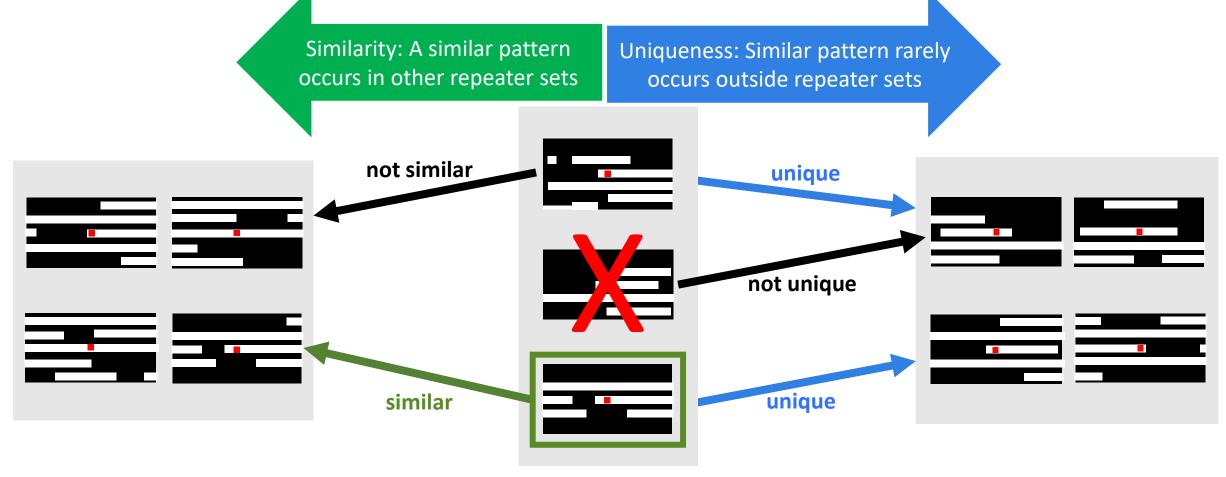

# Grouping of layout patterns – unique and similar

Patterns in other repeater sets

Repeater set of interest (~100 patterns)

Full chip (100s of millions of patterns)

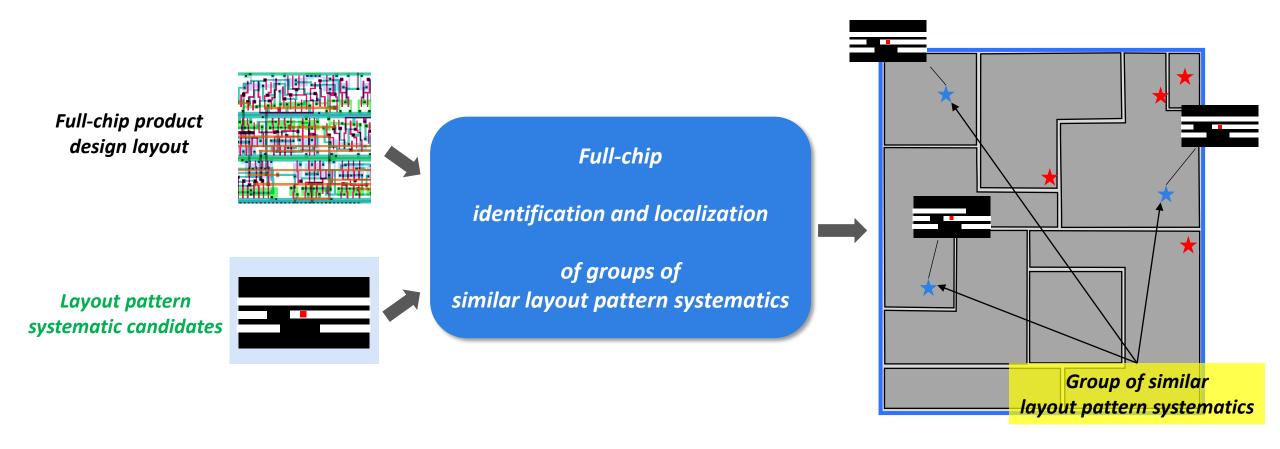

# Full-chip extraction of layout pattern systematics using FIRE

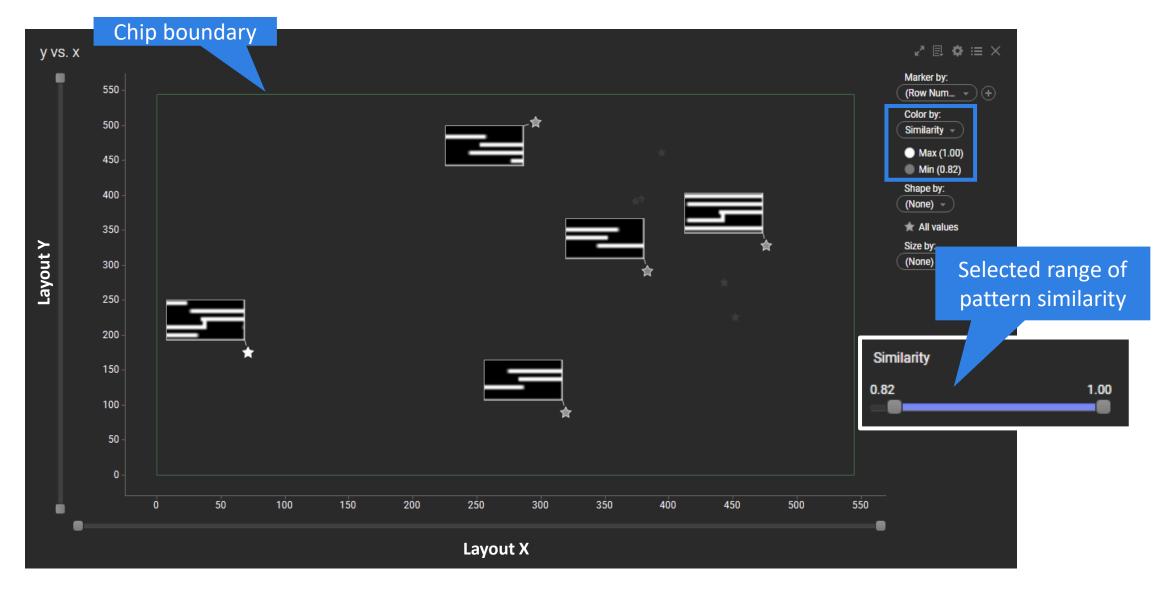

#### Review spatial distribution of layout pattern candidates in Exensio

# **Similarity analysis**

- Uniqueness and similarity analysis are both run across all layers

- Multiple layer interactions are also performed (such as VIA analysis)

- Analysis runs in hours even for large designs

- Volume scan diagnosis data of 2 to 4 lots is sufficient for analysis

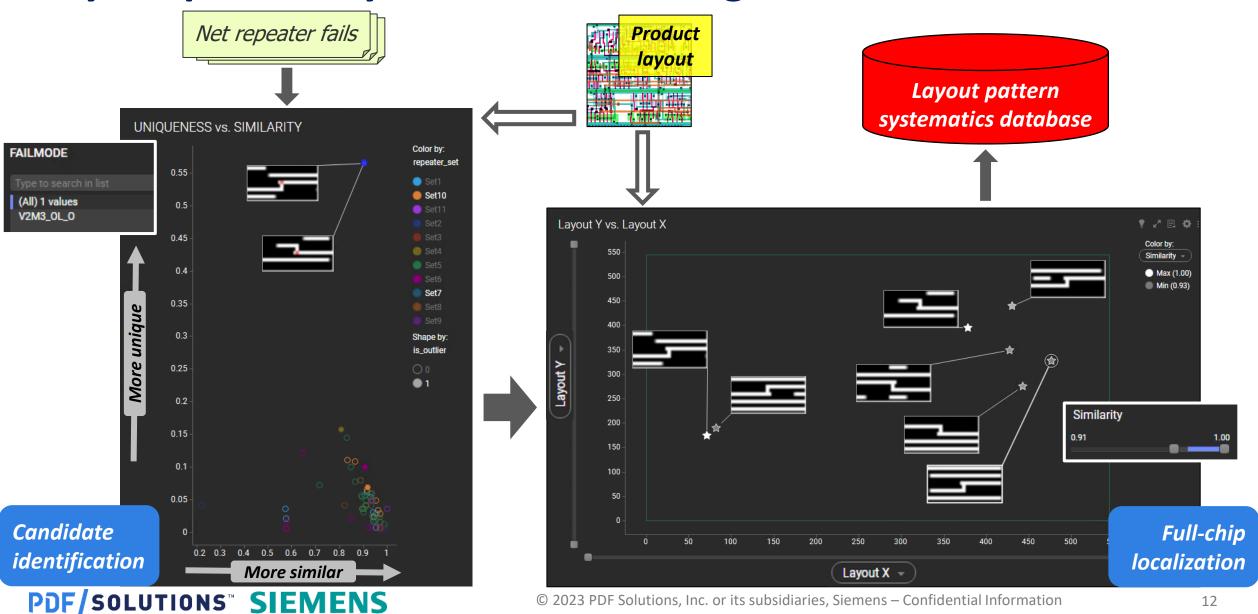

## Layout pattern systematics learning

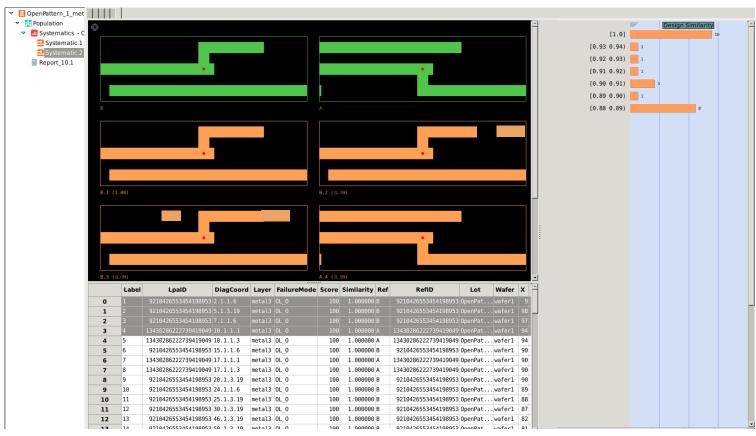

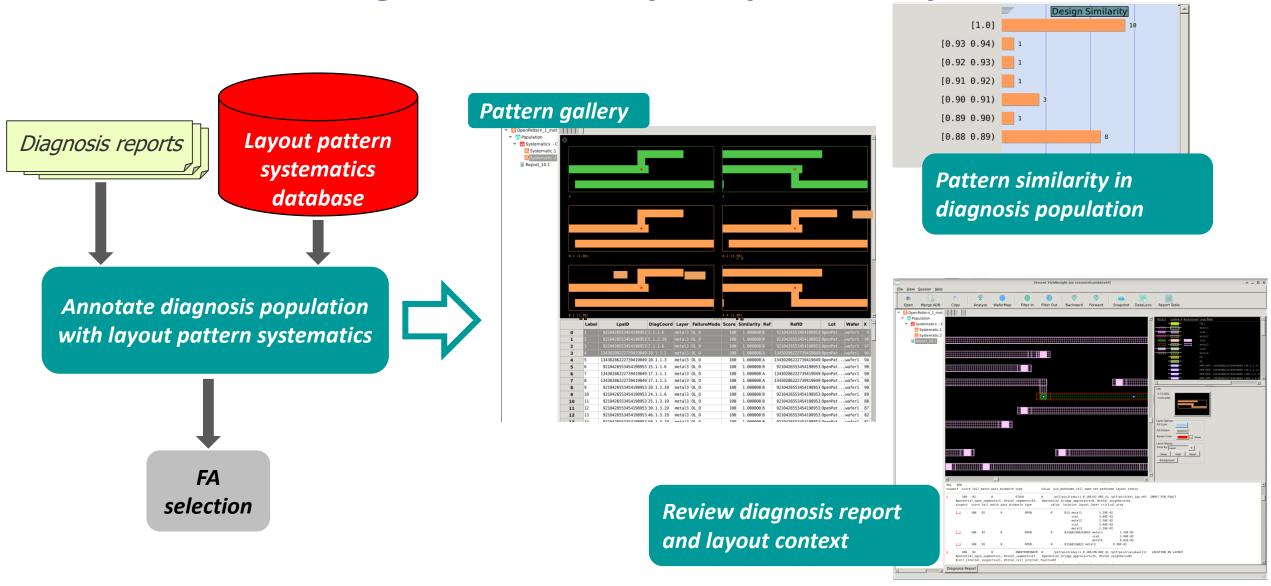

# Overlay on diagnosis reports in Tessent YieldInsight

Pattern gallery to analyze similar patterns in one place

Volume scan diagnosis with layout pattern systematics

#### **Silicon Results**

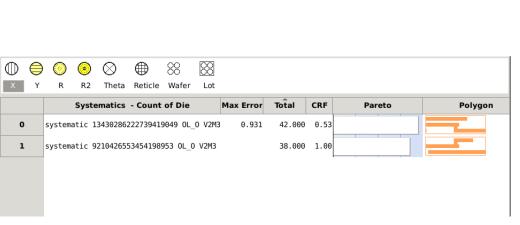

- Successful demonstration on silicon dataset comprising multiple lots/wafers of scan diagnosis data with foundry confirmed layout systematics

- Via opens in two lower metal layers identified as root causes of repeater fails

- 88% of repeater sets attributed to the same two root causes confirmed by FA

- 2 repeater sets had other root causes

- <10 layout patterns per repeater set identified for visual inspection (7X reduction in patterns to be inspected)</p>

- ~65% of repeaters reduced to <=6 patterns for inspection</p>

- Ongoing live silicon engagements with mutual customers on advanced process node

# **Key takeaways**

#### FA today

- 2 or 3 PFAs confirming suspected systematic defect location

- PFA is a destructive process that takes weeks

- Pre cursor to PFA: ATE → Fault isolation ~3-6 weeks per part

- Failure analysis (FI+PFA) costs \$50-100k not accounting for engineering time

- Time to confirm yield issue in PFA and apply corrective action is iterative >4 Months

#### This approach

- Isolation of PFA search area to high confidence locations

- Reduce time for PFA and total number of PFAs for layout pattern systematics

- Improve productivity and quality by making efficient use of FA resources

#### **Overall value**

- Current results demonstrate that identifying layout pattern systematics can be done accurately using scan diagnosis data and layout analysis from FIRE

- Reduced need for FI and FA can further enhance value of this solution for advanced nodes beyond 5nm

- Leverages design information at fabless to improve time-to-market in an increasingly demanding semiconductor market

# Thank you!