**End-to-End Yield Management for Compound Semi**

**Steve Zamek, Dave Huntley, Jon Holt**

May 2025

This presentation and discussions resulting from it may include future product features or fixes, or the expected timing of future releases. This information is intended only to highlight areas of possible future development and current prioritizations. Nothing in this presentation or the discussions stemming from it are a commitment to any future release, new product features or fixes, or the timing of any releases. Actual future releases may or may not include these product features or fixes, and changes to any roadmap or timeline are at the sole discretion of PDF Solutions, Inc. and may be made without any requirement for updating. For information on current prioritizations and intended future features or fixes, contact sales@pdf.com.

PDF Solutions, Exensio, CV, Cimetrix, the PDF Solutions logo, and the Cimetrix logo are registered trademarks of PDF Solutions, Inc. or its subsidiaries. All other trademarks cited in this document are the property of their respective owners. Exensio visualizations Powered by TIBCO®.

© 2025 PDF Solutions, Inc. or its subsidiaries. All rights reserved.

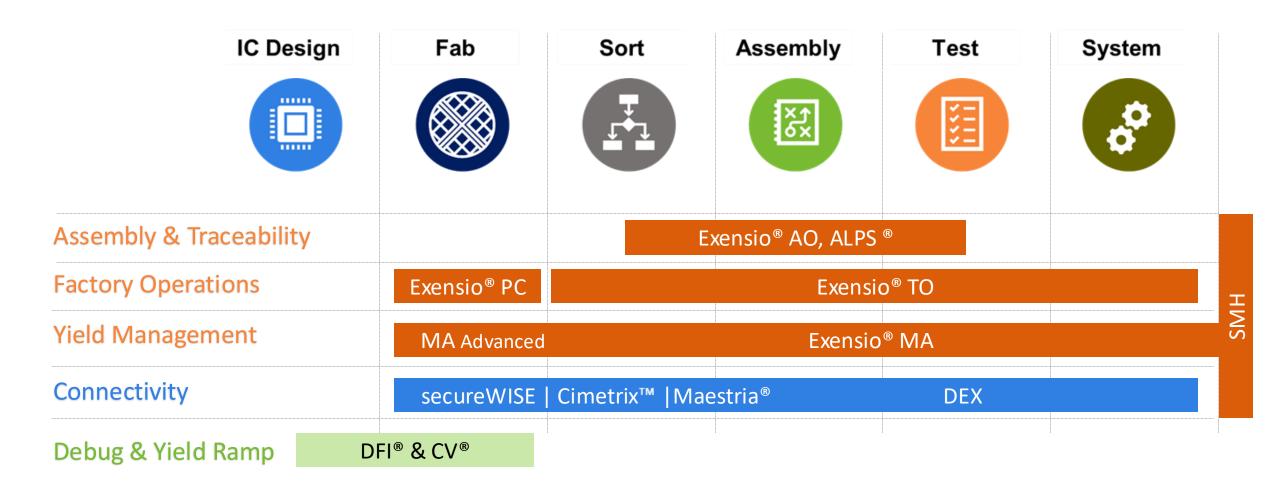

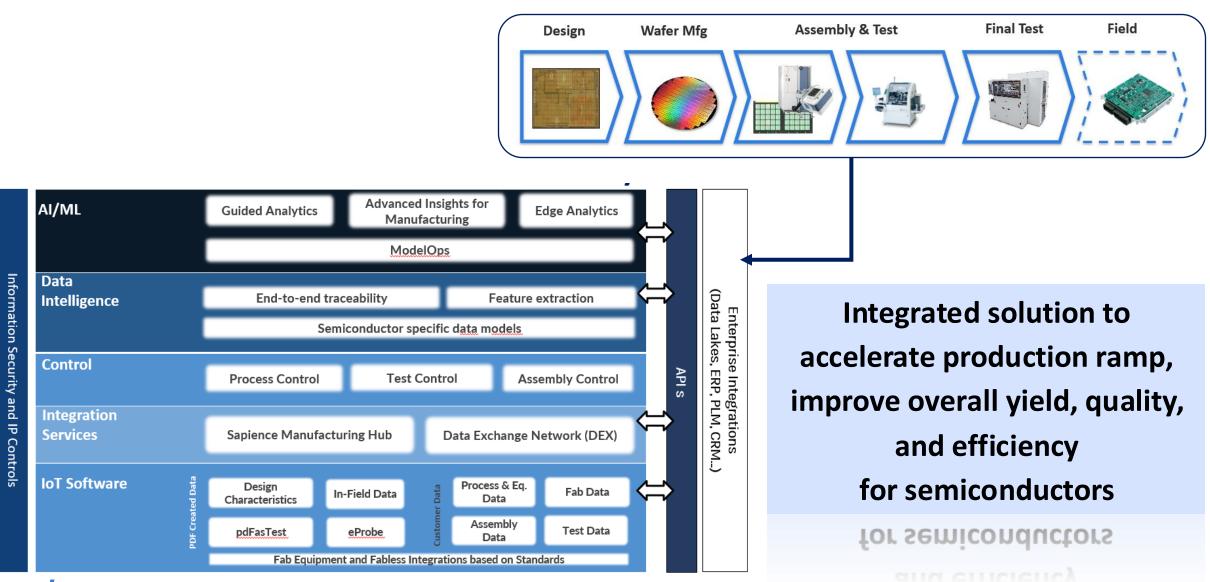

# PDF Solutions: Leading the Digital Transformation of Semiconductor Manufacturing

## **PDF Solutions overview**

# Data Collected in Semiconductor Manufacturing

Design

**Assembly & Test**

**Final Test**

Field

- Design Data

- Chip

- Reticle

- WIP / MES

- Equipment logs & traces

- Lot Genealogy

- Inline

- Metrology

- Inspection

- WAT / PCM

- Wafer Sort

- Bins

- Parametric

- BIT

- Traceability

- Die Bins

- Process Data

- PCB / System **Level Testing**

- In-field monitors

- RMA

### Legend

- BIT: built-in test

- MES: manufacturing exec. sys.

- PCM: process control monitors

- WIP: work in progress

- WAT: wafer acceptance test

- RMA: returned merchandise auth

terabytes of data per day; often 15+ yr retention

# **Customer Base in Compound Semi**

| Select DM's with a focus on compound semi |                                   |              | Fab Technology |              |              |  |

|-------------------------------------------|-----------------------------------|--------------|----------------|--------------|--------------|--|

| Customer                                  | Description*                      | Si           | SiC            | GaAs         | GaN          |  |

| А                                         | In top 10 in Power IC's & modules | ✓            | ✓              |              |              |  |

| В                                         | In top 10 suppliers of RFIC       | ✓            |                | $\checkmark$ |              |  |

| С                                         | In top 10 suppliers of RFIC       | $\checkmark$ |                | $\checkmark$ | $\checkmark$ |  |

| D                                         | In top 5 suppliers of LED's       | $\checkmark$ | ✓              | $\checkmark$ | $\checkmark$ |  |

| Е                                         | In top 10 in Power IC's & modules | $\checkmark$ | $\checkmark$   |              |              |  |

| F                                         | In top 10 in Power IC's & modules | ✓            | ✓              |              | $\checkmark$ |  |

| G                                         | In top 3 GaN DM                   |              |                |              | $\checkmark$ |  |

| Н                                         | In top 10 in Power IC's & modules | ✓            | ✓              |              |              |  |

| 1                                         | In top 10 in ADAS and IoT         | $\checkmark$ | $\checkmark$   |              | $\checkmark$ |  |

| J                                         | In top pure-play foundry for SiC  | ✓            | ✓              |              |              |  |

| K                                         | Niche power IC                    | ✓            | fabless        |              |              |  |

### Notable customers as of 2024-E

Other technologies, (e.g. InP) omitted due to the low wafer volume

Big Data Analytics is deployed in

**12 large manufacturers**

IDM / Fabless / Foundry

+ Material Suppliers

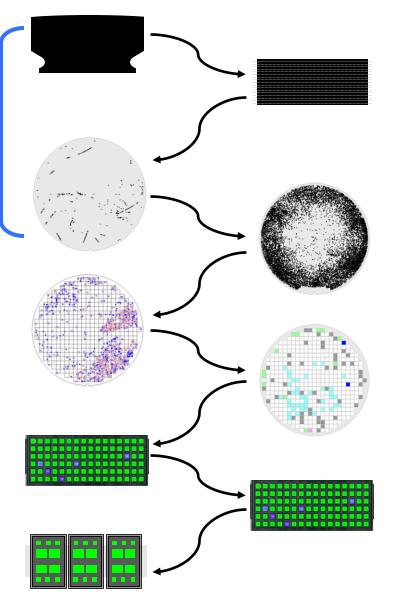

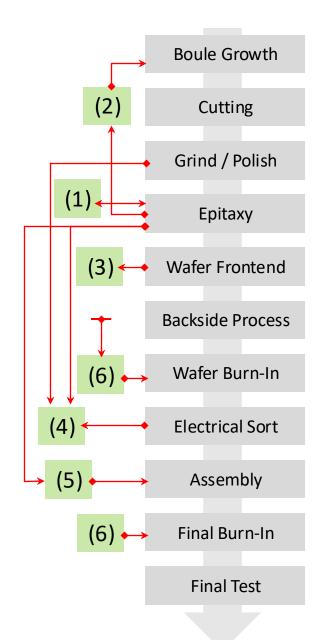

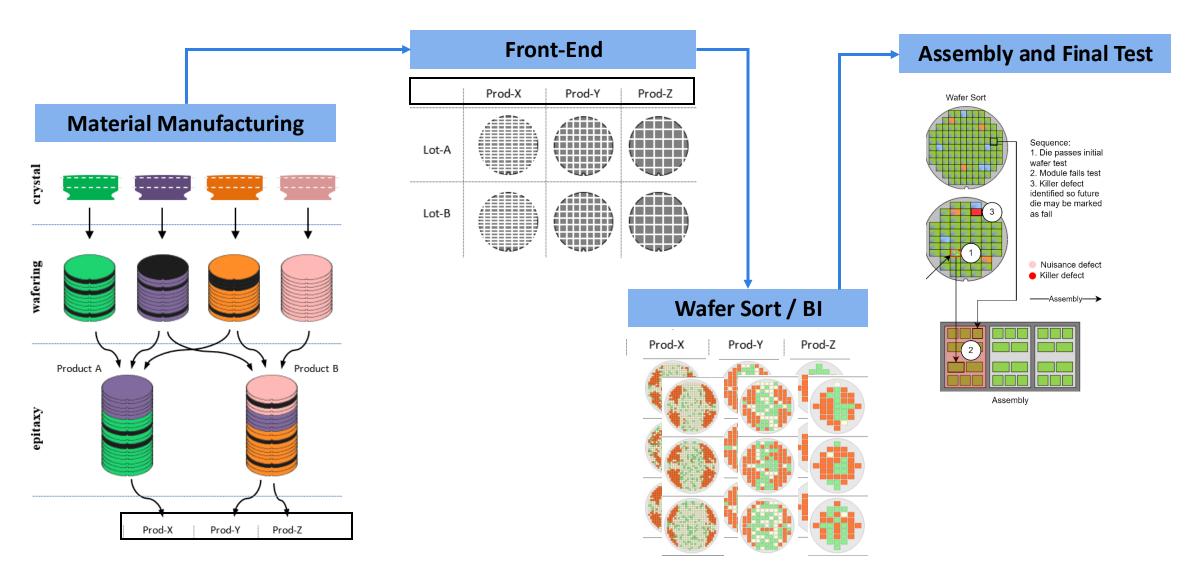

# **Example of SiC Manufacturing**

source: CompoundSemiconductors.net, 2017

source: SICC, 2024

>30% of the final product cost

**Boule Growth**

Cutting

Grind / Polish

**Epitaxy**

Wafer Frontend

**Backside Process**

Wafer Burn-In

**Electrical Sort**

Assembly

Final Burn-In

**Final Test**

# **Examples of End-to-End Analytics**

| # | Use Case                                                   |

|---|------------------------------------------------------------|

| 1 | Defect stacking and re-binning for root-cause analysis     |

| 2 | Reconstructing boule defectivity from epitaxial defects    |

| 3 | Etch process parameters to metrology correlation           |

| 4 | Substrate defect yield impact & Defect Kill ratio analysis |

| 5 | Die screening and ink-out maps for automotive              |

| 6 | Predictive Burn-In based on PCM and Probe data             |

Applying production-proven tools for Compound Semiconductors

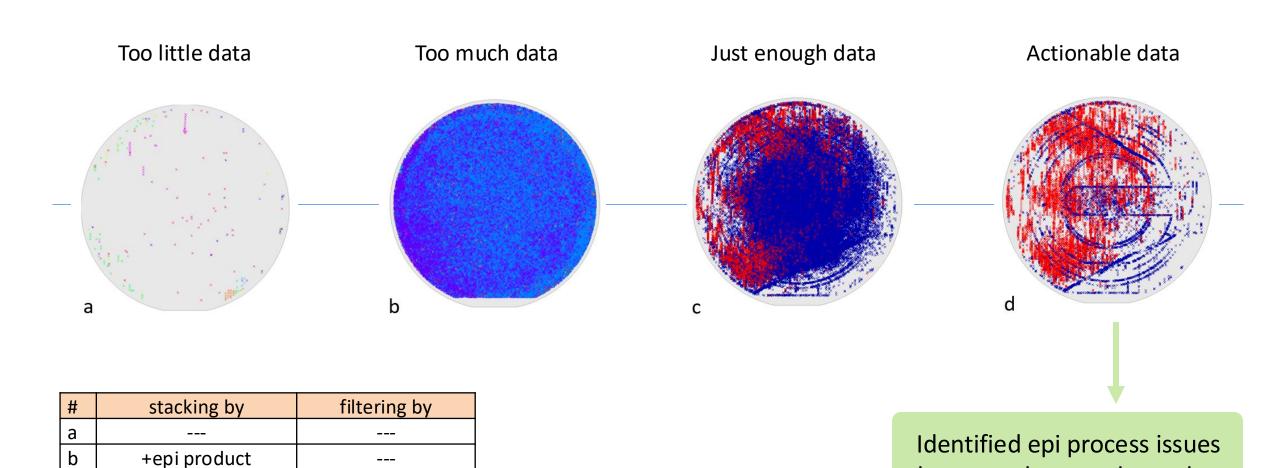

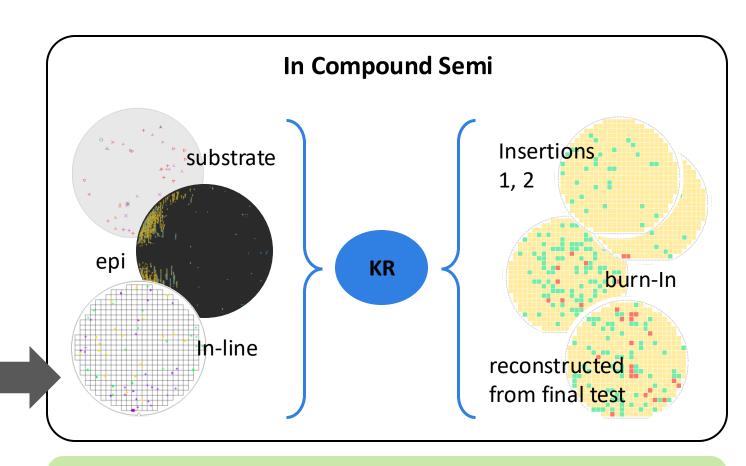

# 1. Defect Management for Root-Cause Analysis

+substrate supplier

+epi reactor

+defect type

+defect size

that are substrate-dependent

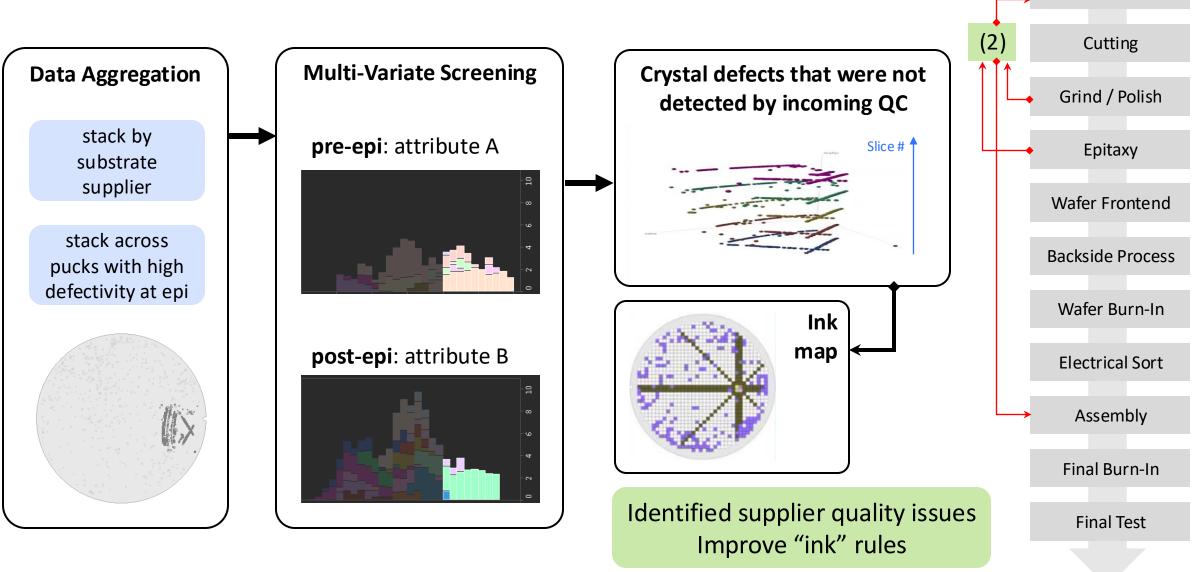

# 2. Puck defectivity from epitaxial defects

**Boule Growth**

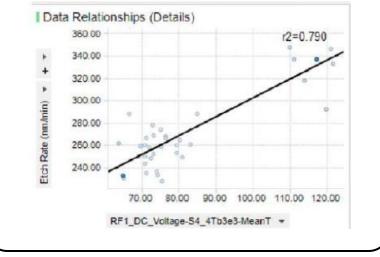

# 3. Etch Parameters to Metrology Correlation

Problem: InP etch exhibits high excursions in etch rate

| Y (numerical)      | X (numerical)                  |     |

|--------------------|--------------------------------|-----|

| Etch Rate (nm/min) | RF1_DC_Voltage-S4_4Tb3e3-MeanT | 1.  |

| Etch Rate (nm/min) | RF1_DC_Voltage-S4_4Tb3e3-Area  | 1,8 |

| Etch Rate (nm/min) | RF1_DC_Voltage-S4_4-Max        | 5.  |

| Etch Rate (nm/min) | RF2_Reflected_Power-S4_4-Area  | 1.  |

| Etch Rate (nm/min) | RF2_Reflected_Power-S4_4-MeanT | 1.  |

| Etch Rate (nm/min) | RF1_DC_Voltage-S4_4-Min        | 1.3 |

| Etch Rate (nm/min) | RF1_Reflected_Power-S3_3-Max   | 2   |

| Etch Rate (nm/min) | RF2_Forward_Power-S4_4Tb3e3-M  | 7.  |

| Etch Rate (nm/min) | Foreline_Pressure-53_4-Max     | 1.  |

| Etch Rate (nm/min) | RF1_Reflected_Power-S4_4-Max   | 3.9 |

| Etch Rate (nm/min) | Helium_Flow-S2_2-Max           | 8.3 |

| Etch Rate (nm/min) | RF1_DC_Voltage-S4_4Tb3e3-StdDe | 1.  |

| Etch Rate (nm/min) | RF1 Reflected Power-S4 4-Area  | 2.5 |

### **Model the Dependency**

### Automated root-cause analysis

- Equipment traces are extracted as indicators

- Indicators correlated to process outcomes

- Excursions in outcomes are tied to the excursions in equipment trace data

# 4. Defect Yield Impact & Defect Kill ratio analysis

### In the Silicon World

|       | PASS | FAIL   |

|-------|------|--------|

| CLEAN | а    | b      |

| DIRTY | C •  | d<br>• |

$$KR = 1 - \frac{Y_D}{Y_C}$$

$$= 1 - \frac{c}{a} \cdot \frac{a+b}{c+d}$$

Complexity / Defectivity / Data Volume / Traceability

→ better models are needed

# 4. Defect Yield Impact & Defect Kill ratio analysis

Using defect maps to predict die state (pass/fail)

### Used for:

- SiC epi substrate grading

- Epi supplier benchmarking

- Substrate-product assignment

# 5. Die screening and ink-out maps for automotive

Probe-Defect Map Ink-out map for assembly Cutting Grind / Polish **Epitaxy** Wafer Frontend **Backside Process** Wafer Burn-In **Electrical Sort** (5)Assembly Passed Clean Passed Defective Final Burn-In Failed Clean Screen-out defective die for yield and quality Failed Defective **Final Test**

**Boule Growth**

# **Under the Hood: Big Data Platform**

# **Under the Hood: Full Traceability**

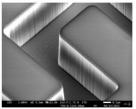

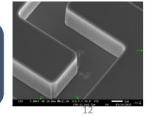

# **Supporting ME Commons & CA DREAMS**

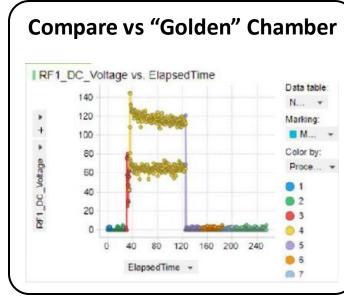

**Two Chambers: Different Physicial Geometry**

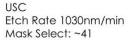

**USC**

Perform InP etch DOEs on Both and measure outputs

Etched at UCSB Etch Rate ~260 nm/min

Etched at USC Etch Rate ~290 nm/min

**Use PDFS Exensio software** to match chambers using DOE results.

Choose GaAs UCSB Recipe **Apply matching from DOE Etch at USC - Compare**

Single Sample **Recipe Transfer** Achieved

**UCSB** Etch rate 1000nm/min Mask select: ~38

Demonstration of a <u>one-shot process transfer</u> between etch tools

# **Final Notes**

- Compound Semi industry is decades behind CMOS in maturity

- But progress can be accelerated using data analytics

Take your next step

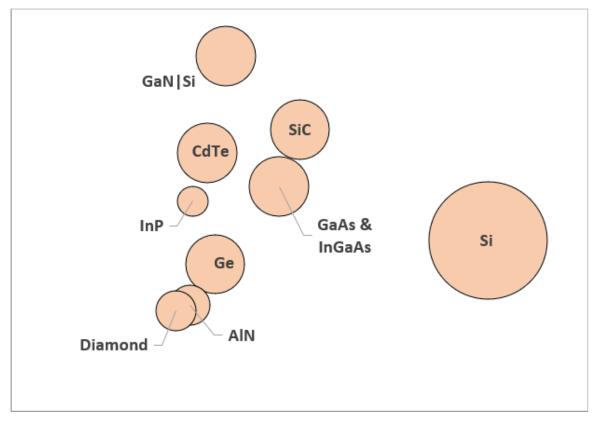

Market Size

# Thank You PDF/SOLUTIONS\*\*

pdf\_solutions

pdfs\_cn