03

A discussion of real-world advanced test methodologies leveraging novel data and AI/ML driven approaches to achieve superior yield, efficiency and device performance.

# Panel Discussion With Advantest, Teradyne, PDF Solutions

SOLUTIONS

This presentation and discussions resulting from it may include future product features or fixes, or the expected timing of future releases. This information is intended only to highlight areas of possible future development and current prioritizations. Nothing in this presentation or the discussions stemming from it are a commitment to any future release, new product features or fixes, or the timing of any releases. Actual future releases may or may not include these product features or fixes, and changes to any roadmap or timeline are at the sole discretion of PDF Solutions, Inc. and may be made without any requirement for updating. For information on current prioritizations and intended future features or fixes, contact sales@pdf.com.

PDF trademarks, including PDF Solutions, Cimetrix, CV, eProbe, Exensio, Sapience, secureWISE, and the logos associated with such brands, are trademarks or registered trademarks of PDF Solutions, Inc. or its subsidiaries. Other trademarks used in this document are the property of their respective owners.

#### PDF/SOLUTIONS°

## Advanced Test In the Semiconductor Industry

2025 USERS CONFERENCE

Dec 3, 2025 www.pdf.com

#### **TERADYNE**

#### **Enabling Advanced Analytics with Archimedes**

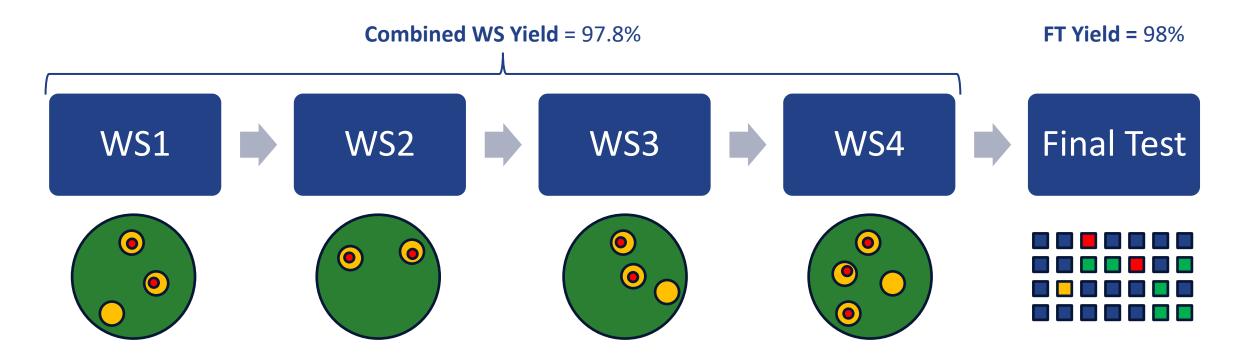

#### FT Fault Predictor

#### **Model Assumptions:**

- Identify a failing die in a 100-die area over kill all 100 die

- Strive for > 90% accuracy

- Overkill 1.6% yield impact

- 1% of Yield Increase at FT

### The "Vmin" App How Machine Learning can help Test Engineers

ACS Product Marketing December 2025

#### The Vmin Test

The Vmin test in semiconductors, determines the minimum operating voltage at which a chip or circuit block can function reliably without errors.

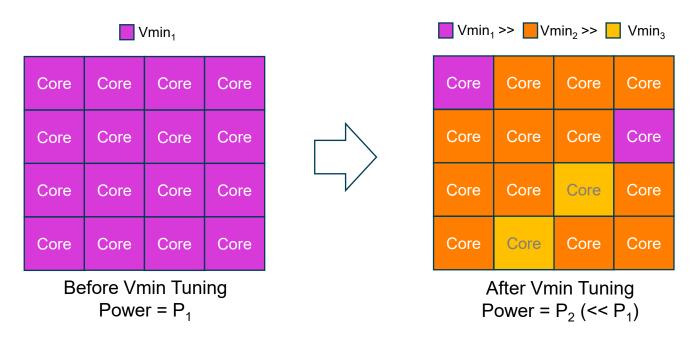

Power Efficiency: lowering operating voltage reduces power, which is vital for mobile, battery-powered devices and also high-performance computing devices.

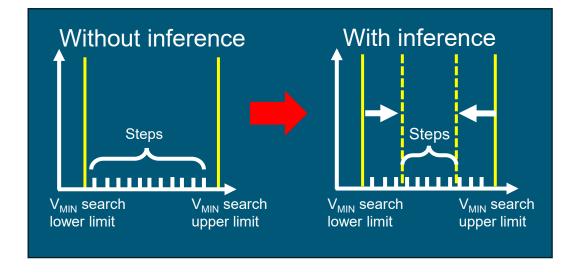

Voltage Sweeping: the supply voltage is gradually reduced during testing while running functional patterns or stress workloads.

#### **How Machine Learning can help Vmin Test**

**Problem:** Extended test duration due to efforts to lower power consumption in multi-core SoCs

**Goal**: Optimize power per core by tuning Vmin without compromising performance, while accelerating Vmin search to reduce overall test time.

**How ML can help**: Utilize ML inferencing to predict likely Vmin per-device and narrow the search limits to speed searches.

**Results**: reduce significantly Vmin test time and at the same time reduce the power consumption of the devices

**Insertion point**: Wafer Sort or Final Test

# Thank You pdf/solutions

www.pdf.com