지난 글에서는 연구의 실험적 측면에 초점을 맞췄습니다. 즉, 고밀도 7nm FinFET 특성 분석 칩, 구조화된 DOE(설계 실험), 그리고 실리콘 상에서 레이아웃에 따른 영향을 분리해 내기 위해 고안된 측정 흐름에 대해 다루었습니다. 하지만 이러한 전기적 결과가 확보되면, 훨씬 더 중요한 질문이 제기됩니다. 바로 레이아웃에 따른 전기적 변화를 어떻게 예측 가능한 물리적 모델로 전환할 수 있을까요?

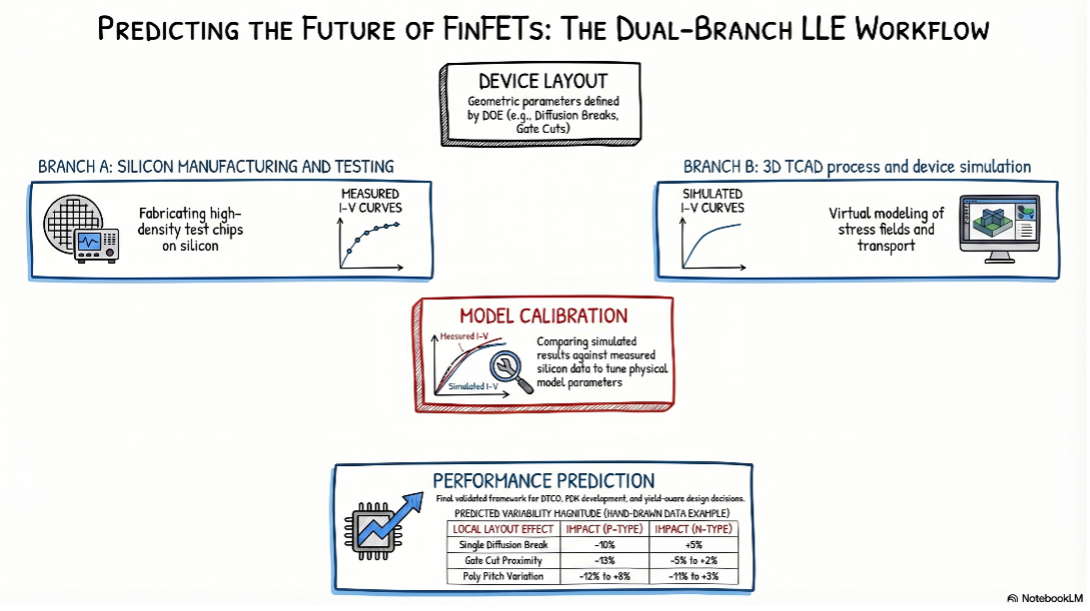

바로 이 점에서 TCAD가 필수적입니다. 실리콘 측정 결과로는 특정 국소 기하학적 구조가 다른 구조와 다른 성능을 보인다는 사실은 알 수 있지만, 왜. 이러한 측정 결과만으로는 근본적인 응력 텐서나 공정으로 인한 변형 분포, 또는 전류나 임계 전압의 관측된 변화에 대한 종방향, 수직, 횡방향 응력 성분의 상대적 기여도를 파악할 수 없습니다. 이러한 수준의 설명과 궁극적으로는 예측을 얻기 위해, 응력 관련 국소 레이아웃 효과(Local Layout Effects)를 모델링한다는 명확한 목표를 가지고 3D TCAD 프레임워크를 구축하고 상용 7nm FinFET 기술의 전기적 데이터와 대조하여 보정했습니다.

그 결과물은 단순히 공칭 트랜지스터에 맞춰 조정된 장치 시뮬레이터에 그치지 않습니다. 이는 국소 기하학적 구조, 공정으로 인한 응력, 이동도 변동, 그리고 전기적 응답을 서로 연결하도록 설계된, 공정 및 레이아웃을 고려하고 실험을 통해 보정된 프레임워크입니다. 이러한 조합 덕분에 이 모델은 설명 용도뿐만 아니라 DTCO, PDK 개발 및 공정 최적화에도 유용하게 활용될 수 있습니다.

이 글에서는 해당 프레임워크가 어떻게 구축되었는지 설명합니다. 즉, 모델이 달성해야 할 목표, 보정 프로세스의 구성 방식, 포함된 물리적 효과, 응력이 전기적 거동으로 어떻게 변환되었는지, 그리고 이러한 유형의 모델링이 첨단 공정 노드의 변동성 분석에 필수적인 이유가 무엇인지 다룹니다.

1. 3D TCAD 모델이 왜 꼭 필요했나요?

인근의 확산 차단(Diffusion Break)이나 게이트 절단(Gate Cut)의 영향을 받는 트랜지스터는 단순히 추상적인 의미에서 “더 좋아지거나” “더 나빠지는” 것이 아닙니다. 국소적인 공정 기하학적 구조가 응력장을 교란시키고, 그 응력장이 실리콘의 이방성 기계적 반응을 통해 전하 운반체의 이동에 변화를 주기 때문에 트랜지스터의 동작이 달라집니다. 전기적 관측에서 물리적 설명으로 나아가고자 한다면, 모델은 레이아웃 기하학적 구조 → 공정으로 인한 응력 → 이동도 변화 → 전기적 특성 간의 연관성을 설명해야 합니다. 이것이 바로 TCAD 프레임워크의 목적입니다.

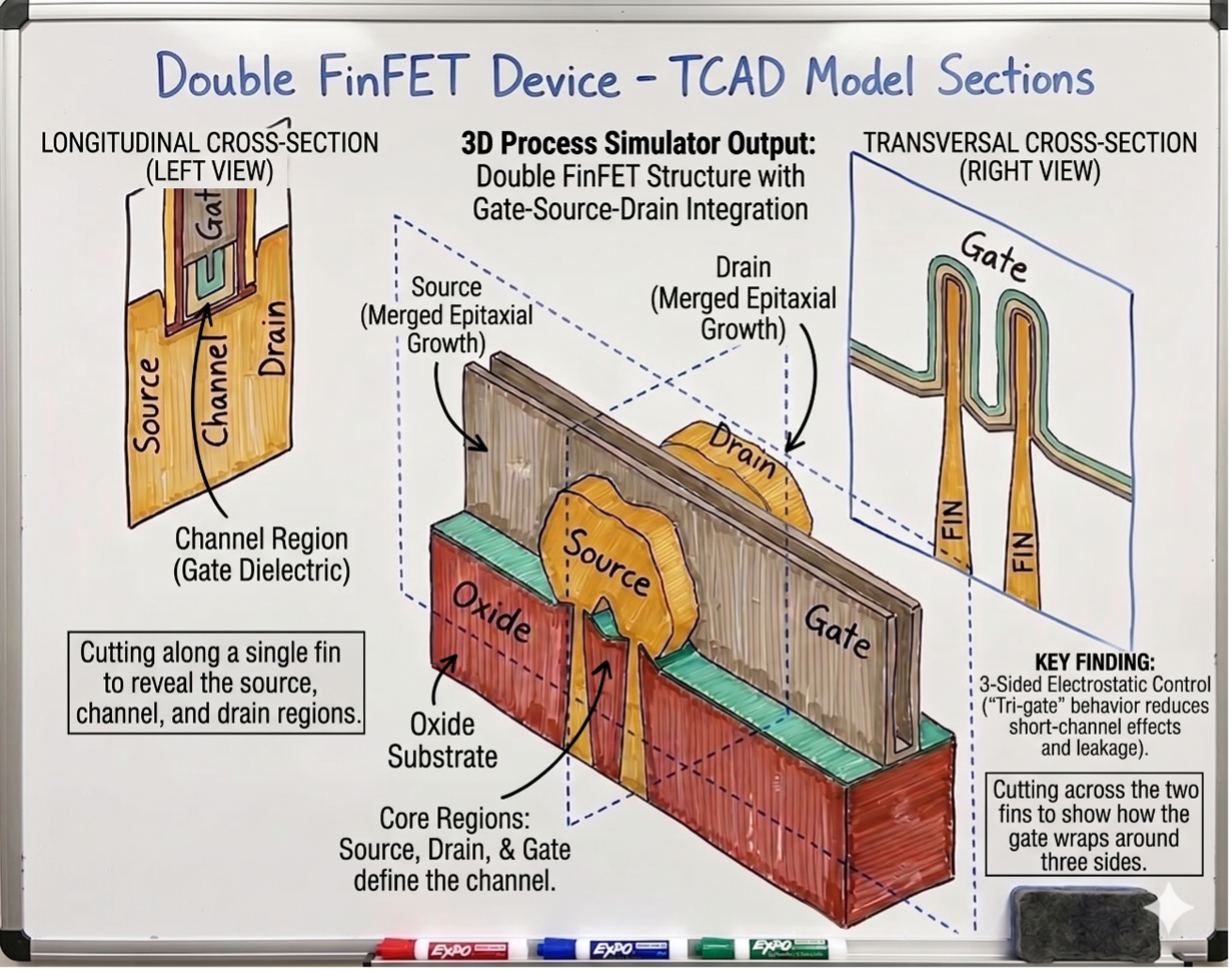

또한 이 프레임워크는 신뢰성을 확보하기 위해 실제 기술과 충분히 근접해야 했습니다. 이는 단순히 하나의 효과를 설명하기 위해 만들어진 단순한 FinFET 모델이 아닙니다. 이 소자 표현은 상용 7nm 실리콘 FinFET 기술을 반영하며, 구조에는 에피택셜 성장, 게이트 스택 형성, 증착 순서 및 열처리에 대한 공정 가정이 포함되어 있다. 응력 관련 LLE는 순수하게 기하학적 인공물이 아니며, 기하학적 구조와 제조 공정 간의 상호작용에서 비롯되므로 이러한 공정 고려는 필수적이다.

모델을 구축해야 하는 세 번째 이유는 실리콘 데이터만으로는 중첩된 메커니즘을 쉽게 분리할 수 없기 때문입니다. 측정 결과 드레인 전류나 임계 전압의 변화가 나타날 수 있지만, 이러한 변화는 여러 상호 연관된 요인에 기인할 수 있습니다. TCAD를 사용하면 응답을 물리적으로 해석 가능한 구성 요소, 즉 국부 응력 텐서, 이동도 변화, 정전기적 변화, 공정 의존적 경계 조건 등으로 분해할 수 있습니다. 이러한 분해가 없다면 LLE 특성 분석은 단순히 현상을 기술하는 수준에 그치게 됩니다. 이를 통해 예측이 가능해집니다.

2. 단순히 곡선 맞추기가 아닌 정확한 예측을 어떻게 보장할 수 있을까?

LLE에 유용한 TCAD 모델은 단순히 하나의 전이 곡선을 재현하는지 여부만으로 판단할 수 없다. 여기서 목표는 더 광범위했습니다. 즉, 다양한 레이아웃 의존적 시나리오에서 측정된 거동을 설명할 수 있고, 이를 통해 설계나 공정 변경의 영향을 예측하는 데 활용될 수 있는 프레임워크를 구축하는 것이었습니다. 그렇기 때문에 이 프레임워크는 제한된 수의 개별 참조 구조가 아닌, 30,000건 이상의 실리콘 측정 데이터로 구축된 데이터셋을 기준으로 검증되었습니다.

이 모델은 특히 확산 차단(DB) 및 게이트 절단(GC) 민감도에 적용되었을 뿐만 아니라, 폴리 피치 및 핀 피치와 같은 관련 기하학적 요인에 따른 효과에도 적용되었습니다. 이 모델은 올바른 추세 방향을 재현할 뿐만 아니라, p형 및 n형 소자 간의 비대칭성도 정확히 포착해야 했습니다. 데이터에 따르면 p형 FinFET은 응력 관련 변동이 대략 ±12%에 달하는 등 훨씬 더 강한 민감도를 보이는 반면, n형 소자는 일반적으로 변동 폭이 더 작으며(종종 5% 미만), 서로 다른 응력 성분들이 상호 경쟁하기 때문에 때로는 비단조적인 거동을 보이기도 한다.

이러한 구별은 모델이 실제로 무엇을 포착하려 하는지 보여주기 때문에 중요합니다. 여기서 핵심 과제는 단순히 “응력이 커지면 전류도 커진다”는 사실을 예측하는 데 그치지 않습니다. 진정한 과제는 물리적 이방성을 띠고 전하 운반체에 의존하는 시스템을 재현하는 것이며, 이 시스템에서는 전기적 반응의 부호와 크기가 소자 내부의 응력 방향과 분포에 따라 달라집니다. 이를 위해서는 프레임워크가 기계적 측면에서 세밀하면서도 전기적 측면에서 정밀하게 보정되어야 합니다.

3. 프로세스 특성을 고려한 3D FinFET 구조를 어떻게 구축할 수 있을까?

모델링 흐름의 출발점은 FinFET의 3D 공정/소자 표현으로, 레이아웃에 민감한 가장 중요한 공정 특징들을 명시적으로 포함할 수 있도록 구성됩니다. 이 모델은 웨이퍼 전체 규모의 변동성이나 전체 제조 공정을 재현하려고 시도하지 않습니다. 대신, 응력 관련 LLEs와 가장 밀접한 관련이 있는 메커니즘인 국소적인 공정 변동성과 국소적 기하학적 효과에 초점을 맞춥니다.

이러한 국소화는 의도된 것입니다. 목표는 가능한 모든 변동 요인을 모사하는 것이 아니라, 충분한 공정 현실성을 갖춘 모델을 구축하는 것 확장 단절(diffusion break) 구성이나 게이트 절단 위치와 같은 특정 레이아웃 선택이 국부 응력 상태와 그에 따른 소자의 전기적 거동을 어떻게 변화시키는지 포착할 수 있도록 하는 것입니다. 이를 위해서는 내장된 에피택셜 영역, 게이트 스택 재료, 유전체 및 절연 구조, 그리고 최종 응력 조건을 생성하는 데 필요한 열 이력을 포함해야 했습니다. 또한 이 프레임워크는 Si/SiGe 재료의 이방성 응력 반응을 반영하고 있는데, 이는 변형이 채널로 어떻게 전파되는지를 추적하는 데 필수적입니다.

실질적으로 이 프레임워크는 두 가지 엔지니어링 계층 사이에 위치합니다. 이 프레임워크는 간소화된 모델보다 물리적 세부 사항이 훨씬 더 풍부하면서도, 레이아웃 민감도 분석 및 기술 탐색에 유용할 만큼 충분히 집중되어 있습니다. 바로 이러한 중간적 위치 덕분에 레이아웃을 고려한 변동성 분석과 DTCO 중심 연구에 효과적인 것입니다.

4. 왜 교정 작업이 두 단계로 나뉘어 진행되었는가?

모델링 과정에서 가장 중요한 결정 중 하나는 보정 작업을 두 단계로 나누는 것이었습니다. 즉, 먼저 공정 보정을 수행한 다음 전기/소자 보정을 진행하는 방식입니다. 이러한 구분은 매우 중요합니다. 왜냐하면 전기적 피팅 작업이 시작되기 전에 구조적 가정을 확고히 정립하지 않으면, 응력 관련 LLE 모델링의 신뢰도가 금세 떨어지기 때문입니다.

공정 보정 단계에서는 기준 트랜지스터의 기하학적 구조와 재료 특성을 확립했습니다. 보정된 구조는 약 7.7 Å의 유효 산화막 두께(EOT)를 포함하며, 이는 약 6 Å의 SiO₂와 11 Å의 HfO₂로 구성된 적층 구조에 해당합니다. 이송 특성 피팅이 시작되기 전에 물리적으로 타당한 기준 모델을 생성하기 위해 다른 구조적 가정값들도 조정되었습니다. 그 후, 인터페이스 트랩 밀도 가정을 사용하여 서브스레숄드 거동을 조정했으며, 드레인 전류는 핀 높이 및 전기 이득 계수 등의 매개변수를 통해 보정되었습니다.

이러한 순차적 접근 방식은 모델이 단순한 곡선 피팅으로 전락하는 것을 방지합니다. 공정 표현이 불안정할 경우, 전기적 파라미터를 강제로 조정하여 측정된 곡선과 일치시킬 수는 있지만, 그 결과는 더 이상 물리적으로 타당한 소자와 부합하지 않을 수 있습니다. 구조적 보정과 전이 보정을 분리함으로써, 최종 모델은 예측 공학 프레임워크로서 훨씬 더 타당한 근거를 갖게 됩니다.

5. 시뮬레이터 내부의 물리 스택은 어떤 모습인가요?

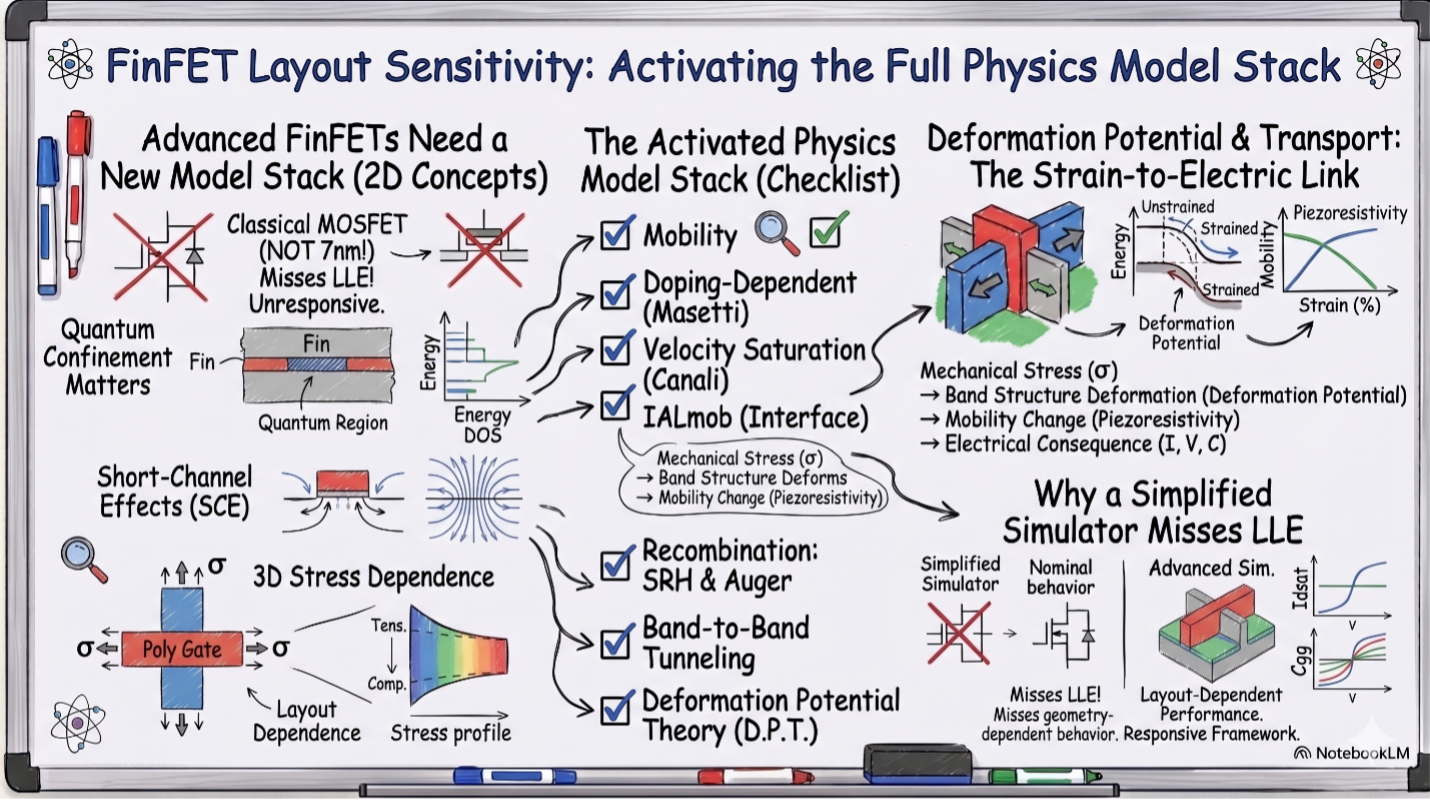

기준 구조가 확립된 후, 다음 단계는 부하 조건 하에서 첨단 FinFET의 동작을 재현하는 데 필요한 물리 모델을 활성화하는 것이었습니다. 시뮬레이터 설정에는 Masetti 도핑 의존성 이동도, Canali 속도 포화, IALMob, 압전 저항성 이동도, Shockley–Read–Hall(SRH) 재결합, Auger 재결합, 밴드 간 터널링, 변형 전위 이론, 상태 밀도 보정 및 밀도 구배 양자 보정이 포함됩니다.

이 모델 스택은 대상 문제가 기존의 장채널 MOSFET이 아니라는 점을 반영합니다. 7nm급 FinFET 노드에서는 서브스레숄드 정전기 현상, 이동도 저하, 양자 제한 효과, 응력 민감형 전도 현상이 모두 중요한 역할을 하며, 이들은 3차원 구조 내에서 상호작용합니다. 변형 전위 기반 물리 모델과 압전저항 이동도 보정의 사용은 특히 중요합니다. 이는 기계적 응력을 전기적 결과로 변환하는 메커니즘이기 때문입니다.

이 모델들이 단순히 완전성을 기하기 위해 포함된 것은 아닙니다. 대상 문제가 본질적으로 레이아웃에 민감하기 때문에 이 모델들이 필요했습니다. 단순화된 시뮬레이터는 트랜지스터의 명목상 동작은 재현할 수 있더라도, 국소적인 기하학적 구조가 변할 때 나타나는 민감도를 완전히 간과할 수 있습니다. 전체 스택을 포함함으로써, 이 프레임워크는 설명하고자 하는 바로 그 효과들에 민감하게 반응할 수 있게 됩니다.

6. 왜 응력 텐서 분해가 진정한 핵심이었을까?

이 전체 프레임워크의 핵심에는 ‘모든 응력이 동일하지는 않다’는 하나의 개념이 자리 잡고 있습니다. 단일 스칼라 응력 값만으로는 현대 FinFET의 관측된 거동을 설명하기에 충분하지 않으며, 특히 n형 소자와 p형 소자 간에 측정된 민감도가 현저히 다른 경우에는 더욱 그렇습니다. 따라서 본 분석에서는 응력장을 주요 구성 요소, 특히 종방향, 수직방향, 횡방향 응력으로 분해하고, 각 구성 요소가 전기적 응답에 어떻게 기여하는지 연구합니다.

이러한 분해 과정을 통해 PMOS와 NMOS 간의 비대칭성을 물리적으로 이해할 수 있습니다. 결과에 따르면, 종방향 응력이 p형 소자의 레이아웃 민감도에 가장 큰 영향을 미치는 것으로 나타났으며, 이는 PMOS 소자가 확산 단절(Diffusion Break) 및 게이트 절단(Gate Cut) 구성에 대해 그토록 강한 의존성을 보이는 이유를 설명해 줍니다. n형 소자의 경우 상황은 더 복잡합니다. 수직 및 횡방향 응력 성분이 더 큰 영향을 미칠 수 있으며, 여러 성분이 서로 부분적으로 상쇄 작용을 일으키기 때문에 전체적인 전기적 응답은 종종 더 작고 단조롭지 않은 양상을 보입니다.

이는 전체 모델링 작업에서 얻은 가장 흥미로운 교훈 중 하나입니다. PMOS의 감도가 더 높다는 사실은 단순히 측정 결과를 통해 얻은 경험적 관찰에 그치는 것이 아니라, 3차원 소자 구조 내부에서 서로 다른 캐리어들이 서로 다른 응력 방향에 어떻게 반응하는지에 대한 물리적으로 해석 가능한 결과로 이어집니다. 바로 이것이 TCAD가 제공할 수 있는 통찰력이며, 측정 결과만으로는 쉽게 밝혀내기 어려운 부분입니다.

7. 실리콘 검증은 어떻게 모델의 신뢰성을 입증했는가?

TCAD 프레임워크는 실리콘 칩의 실제 동작을 재현할 때만 의미가 있습니다. 따라서 3D 모델을 보정하고, 특히 응력 관련 LLE(수명 제한 효과)에 가장 큰 영향을 미치는 레이아웃 시나리오에 중점을 두어 고밀도 측정 데이터셋을 통해 검증했습니다. PMOS 및 NMOS 소자 모두에서 시뮬레이션 결과와 측정값 간의 일치도가 높았으며, 이 프레임워크는 확산 단절(Diffusion Break) 및 게이트 절단(Gate Cut) 민감도와 관련된 주요 경향을 잘 재현합니다.

이 검증 단계는 목표 효과가 항상 크지 않기 때문에 특히 중요합니다. 특히 n형 소자의 경우, 변화 폭이 불과 몇 퍼센트에 불과한 경우도 있습니다. 따라서 더 큰 PMOS 감도와 더 작고 복잡한 NMOS 응답을 모두 재현하는 것은 모델의 신뢰성을 검증하는 의미 있는 테스트입니다. 이는 해당 프레임워크가 단순히 하나의 표준 소자에만 적용되는 것이 아니라, 다양한 소자 극성과 구성에 걸쳐 레이아웃에 따른 물리적 특성을 정확하게 포착하고 있음을 보여줍니다.

바로 이러한 검증 과정을 통해, 이 프레임워크는 이후 더 광범위한 공정 연구에 활용될 수 있게 됩니다. 모델이 측정된 레이아웃 민감도를 재현할 수 있음이 입증되면, 게이트 커팅 타이밍, 유전체 절연재 선택, SDB 트렌치 폭, 스페이서 두께, 온도 등과 같은 요소들을 탐구할 수 있게 되는데, 이러한 요소들은 모든 조합에 걸쳐 실험적으로 분리하여 분석하기에는 훨씬 더 어려운 과제들입니다.

8. 스트레스 물리학은 어떻게 콤팩트 모델로 표현되는가?

이 프레임워크의 가장 큰 장점 중 하나는 단순히 응력 시뮬레이션에 그치지 않는다는 점입니다. 추출된 민감도 값들은 U0, UA, DVTP0, DVTP1, DVTP2, LPE0 등 BSIM-CMG 관련 간소화된 모델 매개변수에 명시적으로 매핑됩니다. 이 단계는 물리학적 연구 결과를 회로 시뮬레이션 및 설계 흐름에 직접적인 영향을 미칠 수 있는 형태로 전환한다는 점에서 중요합니다.

이러한 매핑을 통해 이 연구의 광범위한 중요성이 특히 명확하게 드러납니다. 만약 그 결과가 TCAD 내부에만 머무른다면, 소자 물리학을 이해하는 데는 유용하겠지만 설계 지원 측면에서는 그 유용성이 크게 떨어질 것입니다. 이 프레임워크는 응력에 의한 레이아웃 민감도를 콤팩트 모델 매개변수와 연결함으로써, 레이아웃에 민감한 소자 동작에서 SPICE 호환 회로 영향으로 이어지는 경로를 만들어 냅니다. 이러한 가교 역할은 PDK 개발, DTCO, 변동성 인식 시뮬레이션, 그리고 수율 중심 설계 분석에 꼭 필요한 요소입니다.

이는 이 시리즈 전체의 핵심 메시지 중 하나를 다시 한번 강조해 줍니다. 즉, 고차원 노드에서 레이아웃은 단순한 도면상의 요소가 아닙니다. 이는 설계자들이 매일 사용하는 모델에 결국 반영되어야 하는 물리적 경계 조건입니다. 컴팩트 모델 매핑이 바로 이를 실제로 가능하게 하는 것입니다.

9. 이 프레임워크는 어떤 새로운 기능을 가능하게 했나요?

보정 및 검증이 완료된 후, 이 프레임워크는 단순한 소자 시뮬레이터를 훨씬 뛰어넘는 존재가 되었습니다. 이는 첨단 노드 기술 개발에 있어 직접적으로 중요한 “만약 ~라면?”이라는 질문을 던질 수 있는 수단이 되었습니다. 이 모델은 게이트 커팅 전략, 스페이서 증착 방식, 유전체 절연 재료, SDB 트렌치 폭 변화, 스페이서 두께 변동성, 그리고 온도가 미치는 영향을 평가하는 데 활용되었으며, 이러한 공정 또는 레이아웃 변수들이 각각 스트레스 관련 LLE 거동의 크기를 어떻게 변화시키는지, 때로는 그 부호까지 바꿀 수 있음을 보여주었습니다.

이러한 결과 중 일부는 특히 주목할 만합니다. 분석 결과에 따르면 게이트 커트 타이밍이 스트레스 민감도에 큰 영향을 미칠 수 있으며, 유전체 절연 재료가 PMOS 성능을 크게 향상시키거나 저하시킬 수 있고, SDB 과식각이 NMOS보다 PMOS에 훨씬 더 큰 악영향을 미치며, 온도를 300K에서 375K로 높이면 n형 소자의 LLE 민감도는 약 80%, p형 소자의 LLE 민감도는 약 40% 감소하는 것으로 나타났습니다. 이는 단순한 추상적 관찰이 아니라, 이 프레임워크가 공정 및 집적화 개발 과정에서 실제적인 상충 관계 해결을 어떻게 안내할 수 있는지를 보여주는 사례들이다.

이는 이 모델이 지닌 가장 실질적인 장점 중 하나입니다. 이 모델은 측정된 실리콘 변동성을 실질적인 공정 통찰력으로 전환해 주며, 이는 산업용 반도체 분야에서 TCAD가 제공할 수 있는 가장 명확한 형태의 가치 중 하나입니다.

10. 현행 체계의 본질적인 한계는 무엇인가?

신뢰할 수 있는 모델링 프레임워크는 자신이 무엇을 할 수 있는지만 아니라, 무엇을 할 수 없는지도 명확히 정의해야 합니다. 이 모델은 웨이퍼 전체 규모의 변동성을 모두 시뮬레이션하려 하지 않으며, 일부 공정 가정은 기반이 되는 기술의 독점적 특성으로 인해 여전히 제약받고 있습니다. 이 모델은 전체 팹 환경에서 발생할 수 있는 모든 제조 변동 요인을 재현하는 것보다는, 국소적인 공정 변동, 국소적인 기하학적 변동, 그리고 응력 관련 전기적 민감도에 중점을 두고 있다.

또한 노드 및 파운드리 간 이식성, 측정 오차, 단순화된 응력 표현, 정적 기하학적 가정, 그리고 계산 비용과 관련된 한계점들이 존재합니다. 이는 단순한 부차적인 주의사항이 아닙니다. 이러한 요소들은 이 프레임워크의 현실적인 적용 범위를 규정하며, 이 프레임워크가 강력하지만 한계가 있는 공학 도구로 이해되어야 함을 분명히 보여줍니다. 이 프레임워크는 레이아웃에 의존하는 광범위한 현상을 설명하고 예측할 수 있지만, 실리콘 특성 분석이나 전체 제조 변동성 분석을 대체할 수 있는 만능 도구는 아닙니다.

실제로 이는 이 프레임워크의 강점 중 하나입니다. 이 프레임워크는 모호함 없이 야심 찬 목표를 제시합니다. 이 프레임워크는 첨단 FinFET 소자에서 발생하는 응력 관련 국소 배열 효과(Local Layout Effects)라는 구체적인 문제를 해결하기 위해 설계되었으며, 물리학적 근거를 바탕으로 하면서도 실용적인 방식으로 해당 문제를 다룹니다.

결론

이전 글이 응력 관련 국소 배열 효과(LLE)를 어떻게 측정했는지에 관한 것이었다면, 이번 글은 그 측정 결과를 어떻게 예측 가능한 물리 모델로 전환했는지에 관한 것입니다. 유용한 LLE 모델은 단순히 전기적 곡선을 맞추는 것 이상의 역할을 해야 합니다. 물리적으로 일관성이 있으면서도 실험적으로 검증된 프레임워크 내에서 국소 기하학적 구조, 공정으로 인한 응력, 이방성 캐리어 이동, 그리고 측정된 소자 응답을 서로 연결해야 합니다. 바로 이것이 3D TCAD 흐름이 구축된 목적입니다.

이 프레임워크는 공정 특성을 고려한 3D 핀펫(FinFET) 구조, 2단계 보정 흐름, 풍부한 전이 및 응력 물리 모델 스택을 결합하고 고밀도 실리콘 측정 결과와 대조하여 검증함으로써, 상용 7nm 핀펫 기술에서 레이아웃에 따른 변동성을 이해하기 위한 예측 기반을 제공합니다. 또한 이 프레임워크는 소자 수준의 응력 물리학에서 콤팩트 모델 파라미터로 이어지는 가교 역할을 수행하여, PDK 개발, DTCO, 공정 최적화 및 변동성 고려 설계에 직접적으로 기여합니다.

그리고 일단 그러한 모델이 확립되면, 가장 흥미로운 질문은 다음으로 이어집니다. 실리콘은 가장 강력한 LLE 메커니즘에 대해 실제로 무엇을 알려주는가? 바로 그 지점에서 논의는 자연스럽게 다음 단계로 넘어갑니다.

다음은 무엇일까요?

다음 글에서는 모델링 프레임워크에서 벗어나 주요 결과로 넘어가 보겠습니다. 즉, 측정된 7nm 핀펫(FinFET) 구조에서 ‘Diffusion Breaks’, ‘Gate Cuts’, ‘Poly Pitch’, ‘Fin Pitch’가 전기적 거동에 어떤 영향을 미치는지, PMOS 소자가 NMOS보다 훨씬 더 민감한 이유는 무엇인지, 그리고 측정 결과와 TCAD 분석을 결합했을 때 근본적인 응력 물리학에 대해 어떤 사실이 드러나는지 살펴보겠습니다.