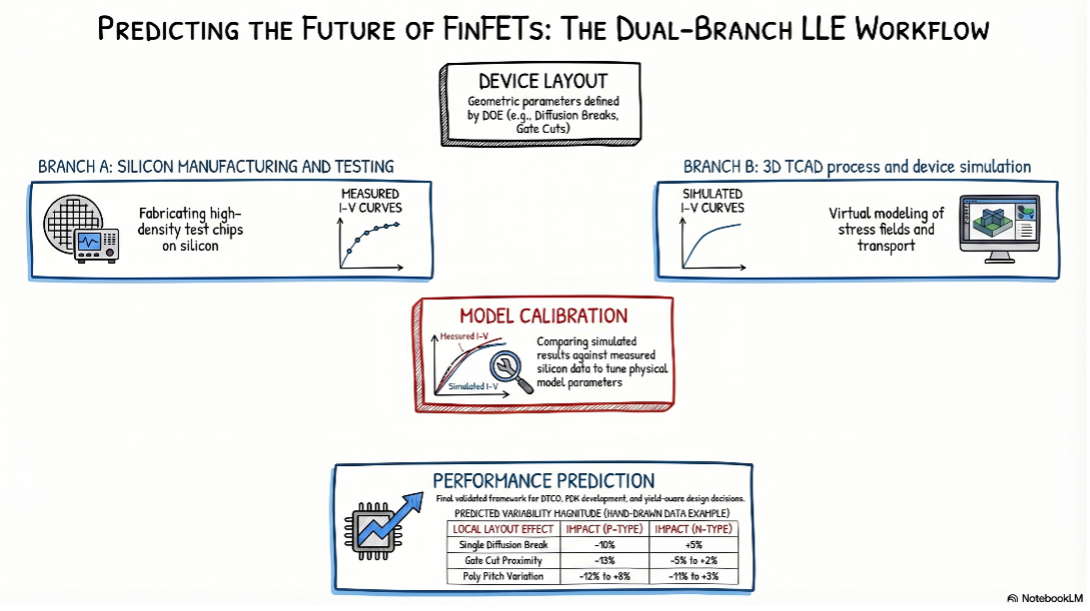

前回の投稿では、この研究の実験的な側面、すなわち高密度7nm FinFET特性評価チップ、構造化DOE、およびシリコン上のレイアウト依存効果を分離するために設計された測定フローに焦点を当てました。しかし、こうした電気的結果が得られた後、さらに重要な疑問が浮かび上がります。それは、レイアウトに依存する電気的変化を、いかにして予測可能な物理モデルへと変換するか、ということです。

そこでTCADが不可欠となります。シリコン測定では、ある局所的な形状と別の形状で動作が異なることは示せますが、 その理由。測定結果からは、根底にある応力テンソルやプロセスに起因するひずみ分布、あるいは観測された電流やしきい値電圧の変化に対する縦方向・垂直方向・横方向の応力成分の相対的な寄与は明らかになりません。そのレベルの説明、ひいては予測を得るために、応力に関連する局所レイアウト効果(LLE)をモデル化するという明確な目標のもと、3D TCADフレームワークが構築され、市販の7nm FinFET技術の電気的データを用いて校正されました。

その結果得られたのは、単なる標準的なトランジスタに合わせて調整されたデバイスシミュレータではありません。これは、プロセスやレイアウトを考慮し、実験的に校正されたフレームワークであり、局所的な幾何学的構造、プロセスに起因する応力、移動度の変動、および電気的応答を結びつけるように設計されています。こうした要素の組み合わせにより、このモデルは説明用としてだけでなく、DTCO、PDK開発、およびプロセス最適化においても有用なものとなっています。

本記事では、そのフレームワークがどのように構築されたかについて解説します。具体的には、モデルが達成すべき目標、キャリブレーションフローの構成、組み込まれた物理的効果、応力が電気的挙動にどのように変換されたか、そしてなぜこの種のモデリングが先進ノードのばらつき解析において不可欠となったのかについて説明します。

1. なぜ3D TCADモデルが不可欠だったのか?

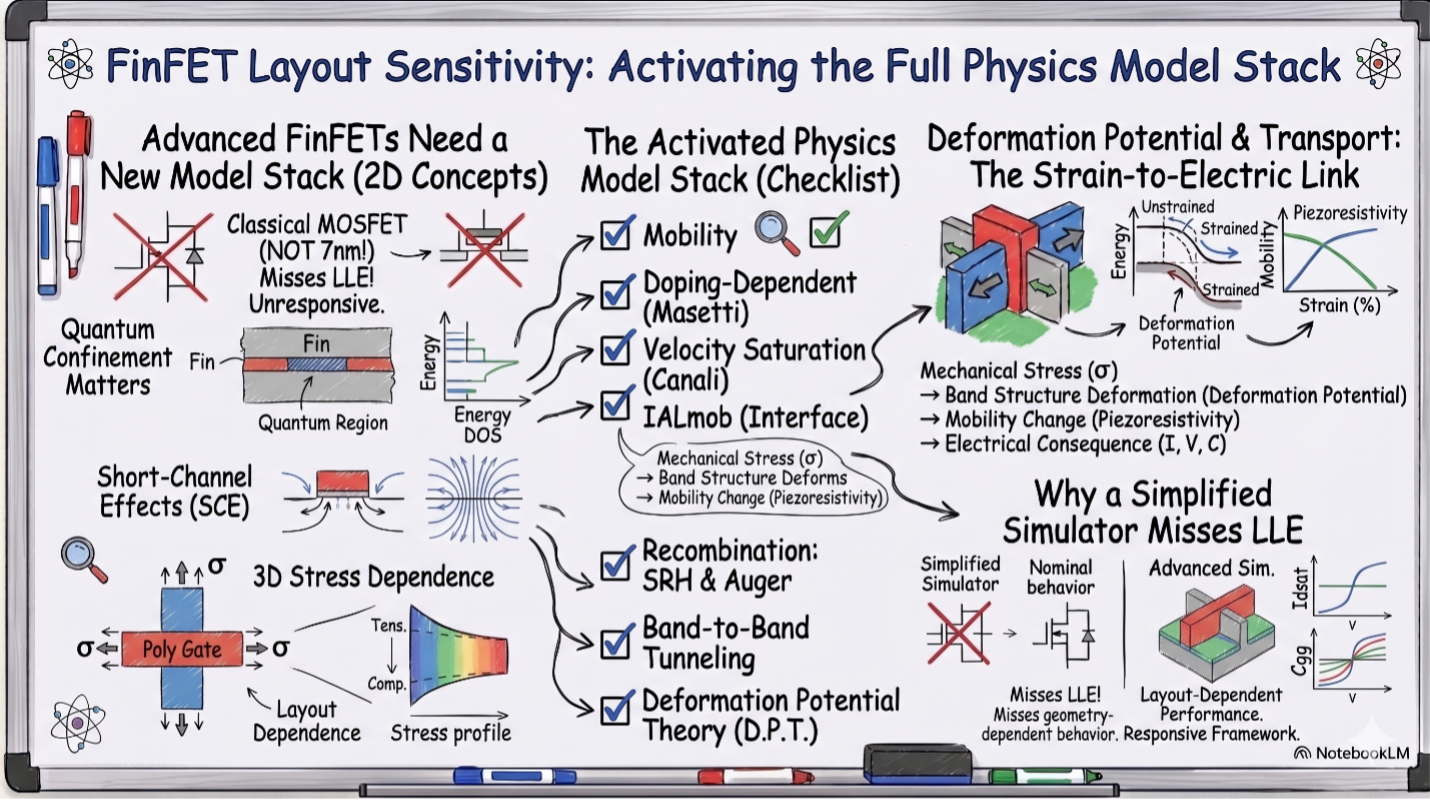

近傍の拡散遮断やゲートカットの影響を受けたトランジスタは、抽象的な意味で単に「良くなる」あるいは「悪くなる」というわけではない。 その挙動が変化するのは、局所的なプロセスジオメトリが応力場を乱し、その応力場がシリコンの異方性機械的応答を通じてキャリア輸送を変化させるためである。電気的観測から物理的説明へと移行することが目的であるならば、モデルは「レイアウトジオメトリ → プロセスによる応力 → 移動度の乱れ → 電気的特性」という連鎖を結びつける必要がある。それこそが、TCADフレームワークの目的である。

また、このフレームワークは、説得力を持つために、実際の技術に十分近いものでなければならなかった。これは、ある現象を説明するためだけに作られた、単なるおもちゃのようなFinFETモデルではない。 このデバイスの表現は、市販の7nmシリコンFinFET技術を反映しており、その構造には、エピタキシャル成長、ゲートスタックの形成、成膜順序、および熱処理工程に関するプロセス上の仮定が含まれている。応力に関連するLLEsは単なる幾何学的アーティファクトではなく、幾何学的形状と製造フローの相互作用から生じるものであるため、こうしたプロセスへの配慮は不可欠である。

モデルを構築する3つ目の理由は、シリコンデータだけでは、重なり合うメカニズムを容易に分離できない点にある。測定結果ではドレイン電流やしきい電圧のシフトが確認されることがあるが、そのシフトは複数の相互に関連する要因によって引き起こされている可能性がある。TCADを用いることで、応答を物理的に解釈可能な要素、すなわち局所応力テンソル、移動度の変化、静電的なシフト、およびプロセス依存の境界条件へと分解することが可能になる。この分解を行わなければ、LLE特性評価はあくまで記述的なものに留まってしまう。 これによって、予測が可能になる。

2. 単なる曲線フィッティングではなく、予測を確実にするにはどうすればよいか?

LLE(低電圧エレクトロニクス)向けの有用なTCADモデルは、単一の転移特性を再現できるかどうかだけで判断することはできない。 ここでの目的は、より広範なものであった。すなわち、レイアウトに依存する複数のシナリオにわたる測定結果を説明し、さらに設計やプロセスの変更による影響を予測するために活用できるフレームワークを構築することである。そのため、このフレームワークは、限られた数の孤立した参照構造ではなく、3万件以上のシリコン測定データから構築されたデータセットを用いて検証されたのである。

このモデルは、特にディフュージョン・ブレイク(DB)およびゲート・カット(GC)の感度特性に適用されたが、ポリピッチやフィンピッチといった関連する形状依存効果にも適用された。このモデルには、正しい傾向の方向を再現するだけでなく、p型デバイスとn型デバイス間の非対称性を捉えることも求められた。 データによると、p型FinFETは著しく強い感度を示し、応力に関連する変動はおよそ±12%に達する一方、n型デバイスは一般的に変動幅が小さく(多くの場合5%未満)、異なる応力成分が互いに競合するため、非単調な挙動を示すことがある。

この区別は、モデルが実際に捉えようとしているものを明らかにする点で重要である。課題は、単に「応力が大きければ電流も大きくなる」と予測することではない。課題は、物理的に異方性があり、キャリアに依存するシステムを再現することであり、そのシステムにおいては、電気的応答の符号と大きさが、デバイス内部の応力の詳細な向きや分解に依存する。そのためには、フレームワークが機械的に詳細であると同時に、電気的にも校正されている必要がある。

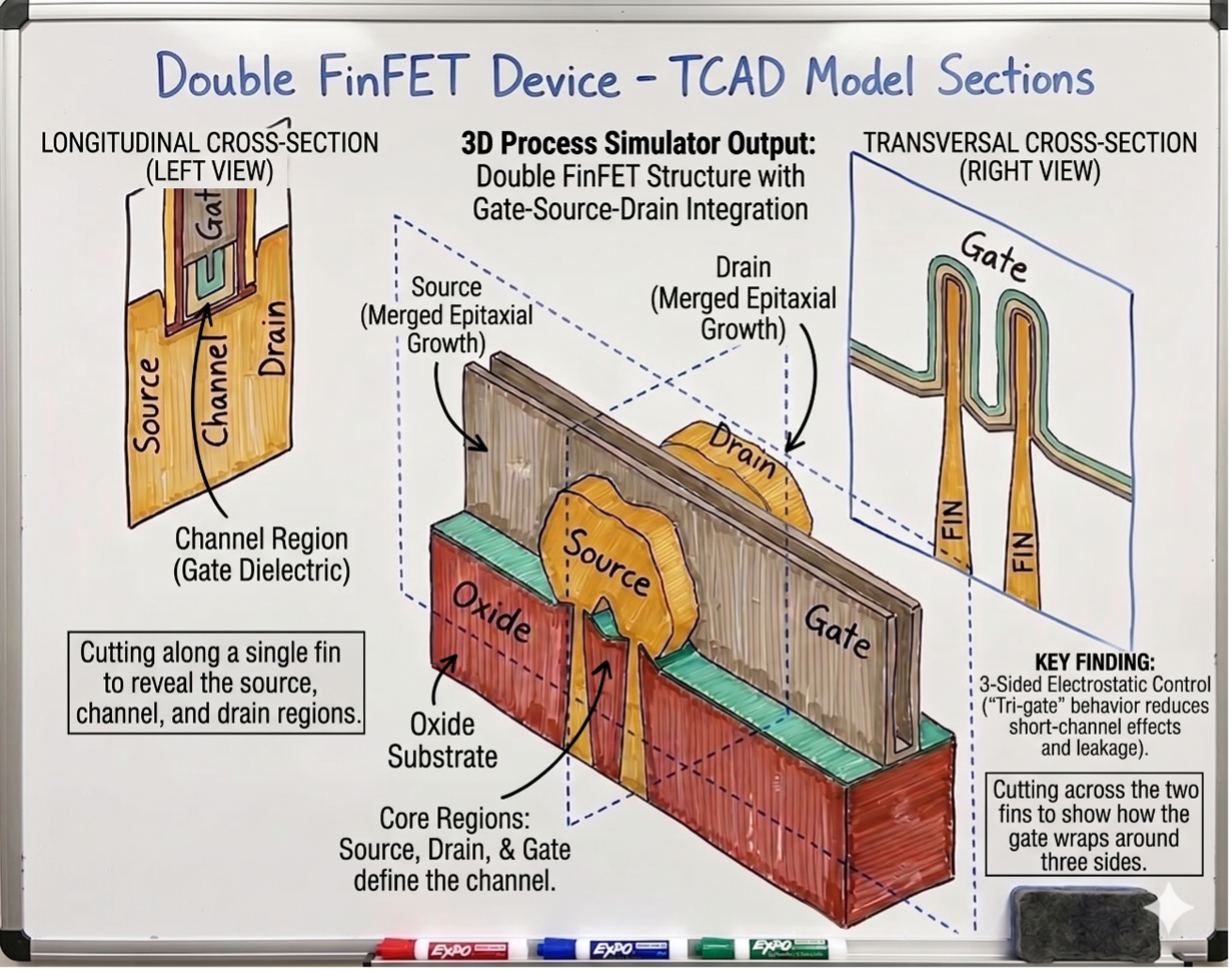

3. プロセスに配慮した3D FinFET構造をどのように構築するか?

モデリングフローの出発点は、FinFETの3Dプロセス/デバイス表現であり、レイアウトに依存する最も重要なプロセス特性を明示的に含められるように構築されています。このモデルは、ウェハ規模の変動性や製造ライン全体を再現しようとするものではありません。その代わりに、応力に関連するLLEsに最も関連性の高いメカニズムである、局所的なプロセス変動や局所的な幾何学的影響に焦点を当てています。

この局所化は意図的なものです。その目的は、考えられるあらゆる変動要因をシミュレートすることではなく、 十分なプロセス現実性を備えたモデルを構築すること モデルを構築し、拡散遮断配置やゲートカット位置といった特定のレイアウト選択が、局所的な応力状態、ひいてはデバイスの電気的挙動をどのように変化させるかを捉えることにある。これには、埋め込みエピタキシャル領域、ゲートスタック材料、誘電体および絶縁構造、そして最終的な応力状態を生成するために必要な熱履歴を含める必要があった。また、このフレームワークにはSi/SiGe材料の異方性応力応答も組み込まれており、これはひずみがチャネル内にどのように伝播するかを追跡するために不可欠である。

具体的には、このフレームワークは2つのエンジニアリング層の間に位置しています。コンパクトモデルよりもはるかに物理的な詳細度が高い一方で、レイアウト感度解析や技術探索に有用なほどに焦点を絞っています。この中間の位置づけこそが、レイアウトを考慮した変動性解析やDTCO(設計・製造・コスト・性能)重視の研究において、このフレームワークを有効なものにしているのです。

4. なぜ校正は2つの明確な段階に分けて実施されたのか?

モデリングのプロセスにおいて最も重要な判断の一つは、キャリブレーションを2つの段階に分けて行うことでした。まずプロセスキャリブレーションを行い、次に電気的/デバイスキャリブレーションを行うという順序です。この分離が重要なのは、電気的フィッティングを開始する前に構造的な仮定を確立しておかないと、応力に関連するLLEモデリングの信頼性が急速に低下してしまうためです。

プロセスキャリブレーション段階では、基準トランジスタの形状および材料モデルが確立された。キャリブレーション済みの構造には、約7.7 Åの有効酸化膜厚(EOT)が含まれており、これは約6 ÅのSiO₂と11 ÅのHfO₂からなる積層構造に相当する。その他の構造上の仮定については、輸送特性のフィッティングを開始する前に、物理的に妥当な基準モデルを作成できるよう調整が行われた。 その後、界面トラップ密度の仮定を用いてサブスレッショルド挙動を調整し、ドレイン電流についてはフィン高さや電気増幅率などのパラメータを通じてキャリブレーションを行った。

この順序付けにより、モデルが単なる曲線フィッティングに陥るのを防ぐことができる。プロセス表現が不安定な場合、電気的パラメータを強制的に測定曲線に合わせることが常に可能ではあるが、その結果はもはや物理的に妥当なデバイスとは一致しなくなる可能性がある。構造的キャリブレーションと輸送的キャリブレーションを分離することで、最終的なモデルは予測工学の枠組みとして、はるかに説得力のあるものとなる。

5. シミュレータ内部の物理モデルはどのようなものか?

基準構造が確立された後、次のステップは、応力下における先進的なFinFETの挙動を再現するために必要な物理モデルを有効化することでした。 シミュレータのセットアップには、Masettiのドーピング依存性移動度、Canaliの速度飽和、IALMob、圧電抵抗性移動度、Shockley–Read–Hall (SRH) 再結合、オージェ再結合、バンド間トンネル効果、変形ポテンシャル理論、状態密度補正、および密度勾配量子補正が含まれています。

このモデルスタックは、対象となる問題が従来のロングチャネルMOSFETではないという事実を反映している。 7nmクラスのFinFETノードでは、サブスレッショルド静電現象、移動度の低下、量子閉じ込め効果、および応力に敏感な輸送現象がすべて重要であり、これらは3次元構造内で相互作用します。変形ポテンシャルに基づく物理モデルとピエゾ抵抗性移動度補正の使用は、機械的応力を電気的結果へと変換するメカニズムであるため、特に重要です。

これらのモデルは、単に網羅性を高めるためだけに組み込まれたわけではありません。対象となる問題が本質的にレイアウトに敏感であるため、これらは不可欠でした。単純化されたシミュレータでは、トランジスタの標準的な挙動は再現できても、局所的な形状が変化した際に現れる感度を完全に見落としてしまう可能性があります。フルスタックを採用することで、このフレームワークは、説明しようとしている影響そのものに適切に対応できるようになります。

6. なぜ応力テンソルの分解こそが真の鍵だったのか?

この枠組み全体の中心にあるのは、「すべての応力が等価であるわけではない」という一つの考え方です。単一のスカラー応力値だけでは、現代のFinFETで観測される挙動を説明するには不十分です。特に、n型デバイスとp型デバイス間で測定された感度がこれほど大きく異なる場合にはなおさらです。したがって、本解析では応力場を主要な成分、特に縦方向、垂直方向、および横方向の応力に分解し、それぞれが電気的応答にどのように寄与しているかを検討します。

この分解により、PMOSとNMOSの非対称性が物理的に理解できるようになります。結果から、p型デバイスのレイアウト感度において縦方向の応力が主な要因であることが示されており、これがPMOSデバイスが拡散ブレークやゲートカットの配置にこれほど強く依存する理由を説明しています。n型デバイスについては、状況はより複雑です。縦方向および横方向の応力成分がより重要になる場合があり、また、複数の成分が互いに部分的に競合するため、正味の電気的応答はしばしば小さくなり、単調性も低下します。

これは、モデリング作業全体を通じて得られた最も興味深い知見の一つです。PMOSの感度がより高いという事実は、単なる測定結果に基づく経験的な観察にとどまらず、3次元デバイス構造内部において、異なるキャリアが異なる応力方向に対してどのように反応するかという物理的メカニズムから導き出される、物理的に解釈可能な結果となっています。これこそが、TCADによって得られる洞察であり、測定だけでは容易に解明できないものです。

7. シリコン・バリデーションは、どのようにしてモデルの信頼性を立証したのか?

TCADフレームワークが意味を持つのは、シリコンデバイスの実際の動作を再現できる場合に限られる。そこで、3Dモデルをキャリブレーションした後、高密度測定データセットを用いて検証を行った。その際、応力に関連するLLEs(低電圧動作限界)に最も影響を与えるレイアウトシナリオに特に重点を置いた。シミュレーションと測定結果の間には、PMOSデバイスとNMOSデバイスの双方において高い一致が見られ、このフレームワークは、拡散ブレークおよびゲートカット感度に関連する主な傾向を再現している。

この検証ステップは、目標とする効果が必ずしも大きくないため、特に重要です。場合によっては、特にn型デバイスにおいて、シフトがわずか数パーセントにとどまることもあります。したがって、感度の高いPMOSと、感度が低くより複雑なNMOSの両方の応答を再現できるかどうかは、モデルの信頼性を測る上で有意義な指標となります。これは、このフレームワークが単一の標準デバイスに適合しているだけでなく、異なるデバイスの極性や構成にわたって、レイアウトに依存する物理的挙動を正しく捉えていることを示しています。

この検証結果こそが、後にこのフレームワークをより広範なプロセス研究に応用することを可能にするものです。モデルが測定されたレイアウト感度を再現できることが確認されれば、ゲートカットのタイミング、誘電体絶縁層の選択、SDBトレンチの幅、スペーサーの厚さ、温度といった要素を検証することが可能になります。これらはすべて、あらゆる組み合わせについて実験的に個別に検証するのは非常に困難なものです。

8. ストレス物理学はどのようにコンパクトモデルへと展開されるのか?

このフレームワークの最も価値ある点の一つは、応力シミュレーションにとどまらないことです。抽出された感度情報は、U0、UA、DVTP0、DVTP1、DVTP2、LPE0など、BSIM-CMGに関連するコンパクトモデルパラメータに明示的にマッピングされます。このステップは、物理的な解析結果を、回路シミュレーションや設計フローに直接反映できる形に変換する点で重要です。

このマッピングこそが、この研究のより広範な重要性が特に明らかになる点である。 もしこの成果がTCADの内部にとどまるだけなら、デバイスの物理的挙動を理解する上では有用であっても、設計の実用化にはあまり役立たないだろう。応力によるレイアウト感応性をコンパクトモデルパラメータと結びつけることで、このフレームワークは、レイアウトに敏感なデバイスの挙動からSPICE互換の回路への影響へと至る道筋を築く。その架け橋こそが、PDK開発、DTCO、変動性を考慮したシミュレーション、そして歩留まり重視の設計解析にまさに必要とされているものである。

これは、本シリーズ全体の主要なメッセージの一つを裏付けるものです。すなわち、高度なノードにおいて、レイアウトは単なる図面上の要素に過ぎないわけではありません。それは、設計者が日々使用するモデルにおいて、最終的には表現されなければならない物理的な境界条件なのです。コンパクト・モデル・マッピングこそが、それを実際に可能にするものです。

9. このフレームワークによって、どのような新たな機能が実現されたのでしょうか?

一度キャリブレーションと検証が完了すると、このフレームワークは単なるデバイスシミュレータ以上の存在となった。それは、先端ノード技術の開発において直接的に重要な「もし~だったら?」という問いを投げかける手段となった。 このモデルを用いて、ゲートカット戦略、スペーサー堆積の選択、絶縁体材料、SDBトレンチ幅の変更、スペーサー厚さのばらつき、および温度が及ぼす影響を評価し、これらのプロセスやレイアウトのパラメータのそれぞれが、応力に関連するLLE挙動の大きさを、場合によってはその符号さえも変化させ得ることを示した。

これらの結果の中には、特に注目すべきものがある。分析の結果、ゲートカットのタイミングがストレス感度に大きな影響を与えること、絶縁材料がPMOSの性能を大幅に改善または悪化させること、SDBの過エッチングがNMOSよりもPMOSにはるかに大きな悪影響を及ぼすこと、そして温度を300 Kから375 Kに上昇させると、n型デバイスではLLE感度が約80%、p型デバイスでは約40%低減することが明らかになった。 これらは単なる抽象的な観察結果ではない。これらは、この枠組みがプロセスおよび集積化開発における実際のトレードオフをどのように導くかを示している。

これは、このモデルの最も実用的な意義の一つです。このモデルは、測定されたシリコンのばらつきを実用的なプロセス知見へと変換します。これは、産業用半導体の分野において、TCADが提供し得る最も明確な価値の一つです。

10. 現行の枠組みにはどのような本質的な限界があるか?

信頼性の高いモデリングフレームワークは、何ができるかだけでなく、何ができないかも明確に定義しなければならない。本モデルは、ウェハ規模の変動性をすべてシミュレートしようとするものではなく、そのプロセスに関する仮定の一部は、基盤となる技術の独自性によって制約を受けている。 本モデルは、ファブ環境全体にわたる製造変動のあらゆる要因を再現することよりも、局所的なプロセス変動、局所的な形状の乱れ、および応力に関連する電気的感度に着目している。

また、ノードやファウンドリの移植性、測定ノイズ、応力の簡略化された表現、静的形状の仮定、および計算コストに関する制約も存在します。これらは単なる付随的な注意点ではありません。これらは本フレームワークの現実的な適用範囲を定義するものであり、本フレームワークが強力ではあるものの限界のある工学ツールとして理解されるべきであることを明確にしています。本フレームワークは、レイアウトに依存する幅広い影響を説明・予測することはできますが、シリコン特性評価や製造変動性の包括的な分析に取って代わる万能なツールではありません。

実際、そこがこの枠組みの強みの一つである。この枠組みは、曖昧さを伴わずに野心的なものである。高度なFinFETデバイスにおける応力関連の局所レイアウト効果という特定の問題を解決するために構築されており、物理的な根拠に基づいた実用的な方法でその問題に取り組んでいる。

結論

前回の投稿が、応力に関連する局所レイアウト効果(LLE)の測定方法についてだったとすれば、今回の投稿は、それらの測定結果をどのように予測可能な物理モデルへと変換したかについてです。 有用なLLEモデルは、単に電気的特性曲線に適合させるだけでは不十分です。局所的な形状、プロセスによる応力、異方性キャリア輸送、そして測定されたデバイス応答を、物理的に整合性が取れており、かつ実験的に検証された枠組みの中で結びつける必要があります。3D TCADフローは、まさにその目的のために構築されたものです。

プロセス特性を考慮した3D FinFET構造、2段階のキャリブレーションフロー、充実した輸送・応力物理モデルスタック、および高密度シリコン測定データとの検証を組み合わせることで、このフレームワークは、商用7nm FinFET技術におけるレイアウト依存のばらつきを理解するための予測基盤を提供します。 また、デバイスレベルの応力物理からコンパクトモデルパラメータへの橋渡しを行うことで、本研究はPDK開発、DTCO、プロセス最適化、およびばらつきを考慮した設計に直接的に寄与するものです。

そして、そのようなモデルが確立されれば、次に最も興味深い問いとなるのは、「シリコンは最強のLLEメカニズムについて、実際にどのようなことを明らかにしてくれるのか」という点だ。議論は自然とそこへと進むことになる。

次は何が待っているのか

次回の記事では、モデリングの枠組みから、主な結果へと話を進めます。具体的には、測定された7nm FinFET構造において、ディフュージョン・ブレイクス、ゲート・カット、ポリ・ピッチ、フィン・ピッチが電気的挙動にどのような影響を与えるか、PMOSデバイスがNMOSよりもはるかに感度が高い理由、そして測定とTCAD解析を組み合わせることで、その根底にある応力物理についてどのようなことが明らかになるかについて解説します。