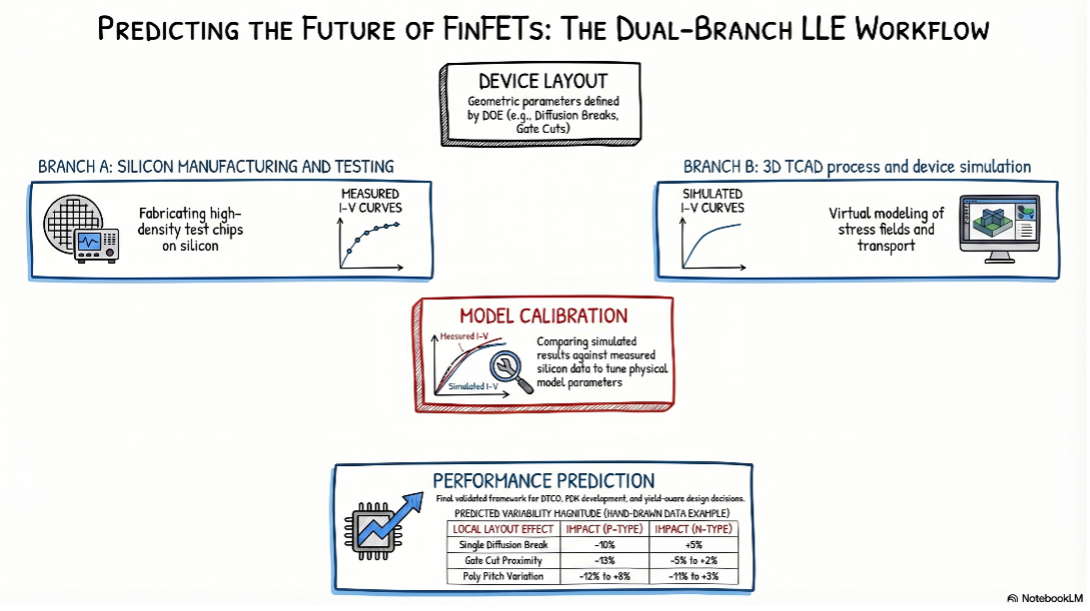

上一篇文章重点介绍了该工作的实验部分:一款高密度7纳米FinFET特性分析芯片、一个结构化设计实验(DOE),以及一套旨在隔离硅片上布局相关效应的测量流程。但一旦获得了这些电学结果,一个更为关键的问题便随之浮现:如何将布局相关的电学变化转化为可预测的物理模型?

正因如此,TCAD 才显得至关重要。硅片测量虽然可以显示不同局部几何结构的性能存在差异,但并不能直接揭示 原因。这些测量无法揭示底层的应力张量、工艺诱导的应变分布,也无法说明纵向、垂直和横向应力分量对观测到的电流或阈值电压变化的相对贡献。为了获得这一层面的解释,并最终实现预测,我们构建了一个三维TCAD框架,并基于商用7nm FinFET技术的电学数据对其进行了校准,其明确目标是建模与应力相关的局部布局效应。

其结果不仅仅是一个针对标称晶体管进行调校的器件仿真器。这是一个兼顾工艺和布局、并经过实验校准的框架,旨在将局部几何结构、工艺诱导应力、迁移率扰动以及电学响应联系起来。正是这种结合,使得该模型不仅适用于理论解释,还可用于数字拓扑控制优化(DTCO)、工艺设计套件(PDK)开发以及工艺优化。

本文阐述了该框架的构建过程:该模型需要实现什么目标、校准流程是如何组织的、纳入了哪些物理效应、应力是如何转化为电学行为的,以及为何此类建模已成为先进工艺节点变异性分析中不可或缺的一部分。

1. 为什么必须使用3D TCAD模型?

受到附近扩散中断或栅极切割影响的晶体管,并非仅仅在抽象意义上变得“更好”或“更差”。 其行为发生变化,是因为局部工艺几何结构扰动了应力场,而该应力场通过硅材料的各向异性机械响应,进而改变了载流子的传输特性。如果目标是从电学观测转向物理解释,那么模型必须建立起布局几何 → 工艺诱导应力 → 迁移率扰动 → 电学特性的关联。这正是TCAD框架的宗旨所在。

该框架还必须与实际技术保持足够接近,以确保其可信度。这并非仅为说明某一效应而构建的简易FinFET模型。 该器件模型反映了商用7纳米硅FinFET技术,其结构包含关于外延生长、栅极堆栈形成、沉积顺序及热处理步骤的工艺假设。这种对工艺的考量至关重要,因为与应力相关的临界电位(LLEs)并非纯粹的几何伪影;它们源于几何结构与制造流程之间的相互作用。

构建该模型的第三个原因是,仅凭硅片数据难以轻易区分相互重叠的机制。测量结果可能显示漏极电流或阈值电压发生了偏移,但这种偏移可能是多种耦合因素共同作用的结果。TCAD技术能够将响应分解为可从物理角度解释的组成部分:局部应力张量、迁移率变化、静电偏移以及与工艺相关的边界条件。如果没有这种分解,LLE表征仍仅停留在描述性层面。 有了这种分解,表征便具有了预测性。

2. 我们如何确保进行预测,而非仅仅是曲线拟合?

一个适用于LLEs的有用的TCAD模型,不能仅凭其能否再现一条转移曲线来评判。 此处的目标更为广泛:构建一个能够解释多种布局相关场景下实测行为的框架,并借此预测设计或工艺变更带来的影响。正因如此,该框架的验证是基于由超过30,000个硅片测量数据构建的数据集进行的,而非仅针对一组孤立的参考结构。

该模型主要应用于扩散中断(DB)和栅极切割(GC)敏感性分析,同时也适用于聚合物间距和鳍片间距等相关几何依赖效应。它不仅需要准确再现趋势方向,还需捕捉p型与n型器件之间的非对称性。 数据表明,p型FinFET表现出显著更强的敏感性,应力相关的波动幅度可达约±12%,而n型器件通常表现出较小的偏移(往往低于5%),且有时会出现更多非单调行为,这是因为不同的应力分量之间相互竞争所致。

这一区别至关重要,因为它揭示了该模型真正试图捕捉的内容。挑战不仅在于预测“应力越大,电流越大”,更在于重现一个物理上各向异性且载流子依赖的系统——在此系统中,电响应的正负与大小取决于器件内部应力的具体取向及其分解情况。这要求该框架在力学上既要细致入微,在电学上又要经过校准。

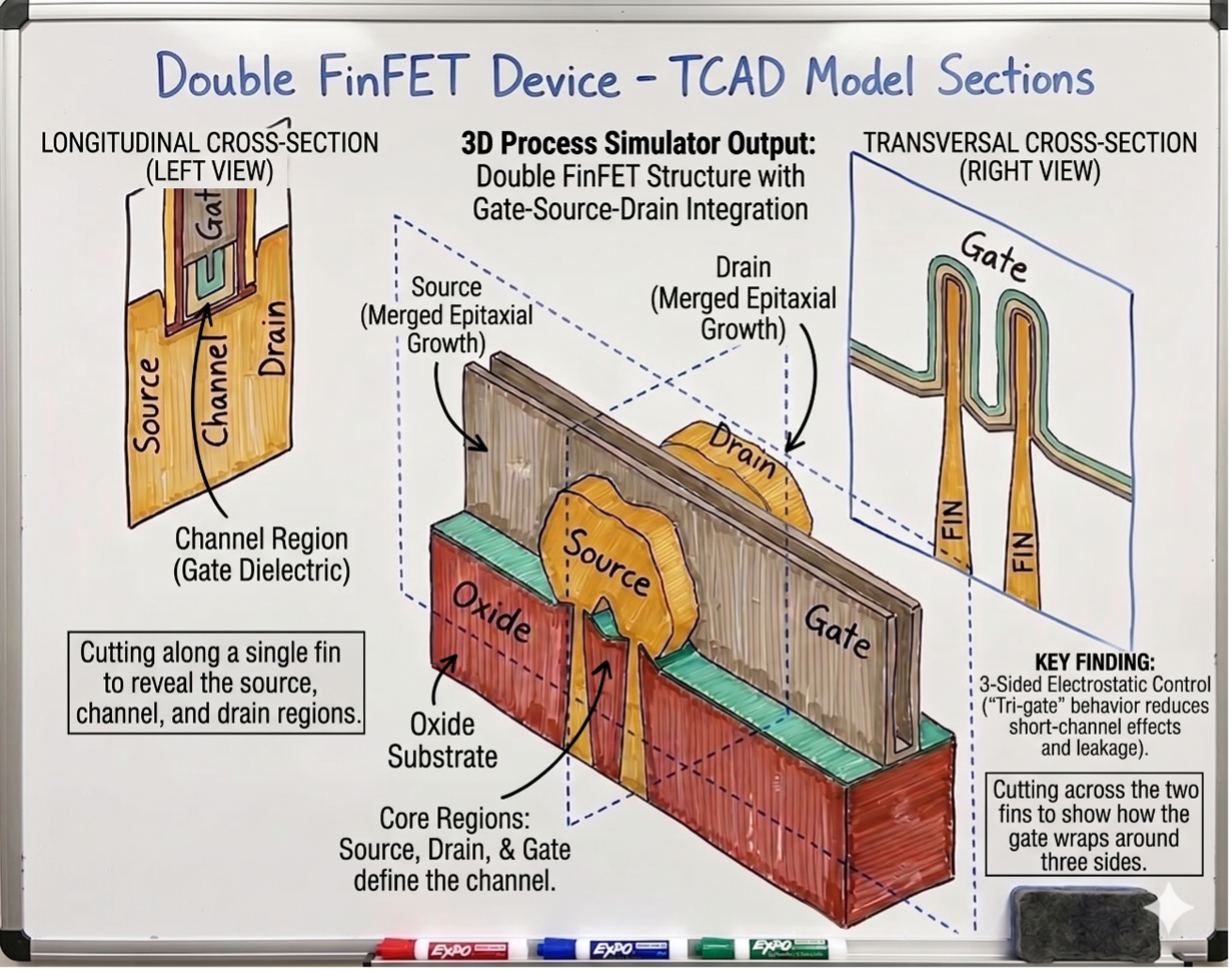

3. 如何构建一种具有工艺意识的3D FinFET结构?

建模流程的起点是FinFET的3D工艺/器件模型,该模型的设计旨在明确纳入与布局相关的关键工艺特征。该模型并不试图再现完整的晶圆级变异性或整个制造生产线,而是专注于局部工艺变异性和局部几何效应,因为这些机制与应力相关的LLEs最为相关。

这种局部化是刻意为之的。其目的并非模拟所有可能的变异来源,而是构建 一个具有足够工艺真实性的模型 ,从而捕捉特定的布局选择——例如扩散中断配置或栅极切割位置——如何改变局部应力状态,进而影响器件的电学行为。这需要纳入嵌入式外延区、栅极堆栈材料、介质和隔离结构,以及形成最终应力状态所需的热历史。该框架还整合了Si/SiGe材料的各向异性应力响应,这对追踪应变如何向沟道传播至关重要。

从实际应用来看,该框架位于两个工程层之间。它在物理细节上远比紧凑模型更为丰富,但仍保持了足够的聚焦度,因此可用于布局敏感性研究和技术探索。正是这种中间定位,使其在布局感知变异性分析和面向数字技术控制优化(DTCO)的研究中发挥了显著作用。

4. 为什么将校准分为两个不同的阶段?

在建模流程中,最重要的决策之一是将校准工作分为两个阶段:首先进行工艺校准,然后进行电气/器件校准。这种分离至关重要,因为如果在开始电气拟合之前未先确定结构假设,与应力相关的LLE建模将很快变得不可靠。

工艺校准阶段确定了参考晶体管的几何结构和材料模型。校准后的结构具有约7.7 Å的有效氧化层厚度(EOT),对应于约6 Å的SiO₂和11 Å的HfO₂组成的氧化层堆叠。在开始输运拟合之前,对其他结构假设进行了调整,以建立一个物理上合理的参考模型。 随后,通过界面陷阱密度假设对亚阈值行为进行了调整,同时通过鳍高和电增益因子等参数对漏极电流进行了校准。

这种排序方式可防止模型退化为单纯的曲线拟合。如果过程表征不稳定,虽然可以强行使电学参数与测量曲线相匹配,但结果可能不再对应于一个在物理上合理的器件。通过将结构标定与输运标定分离,最终模型作为预测性工程框架的可信度将大大提高。

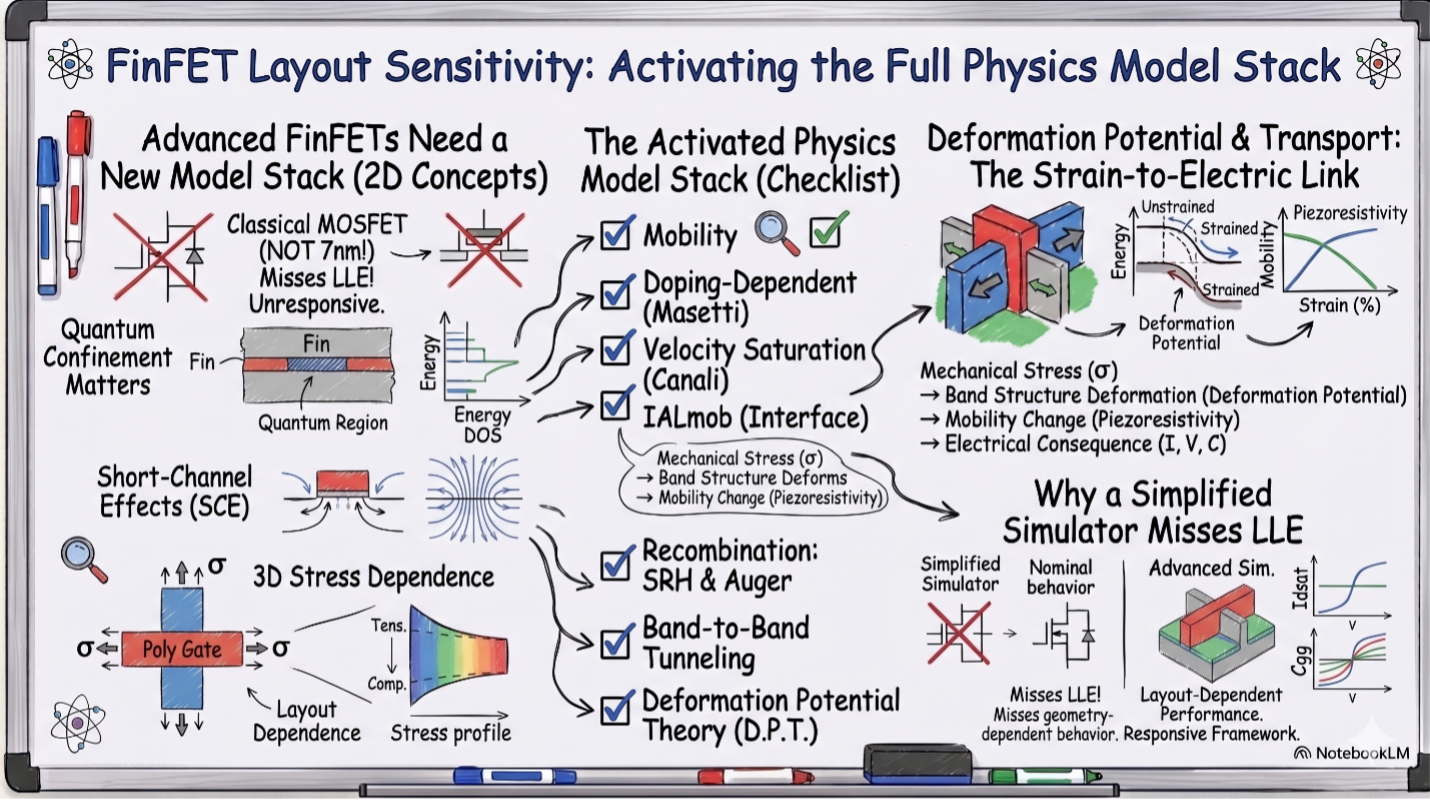

5. 模拟器内部的物理引擎是怎样的?

建立参考结构后,下一步是激活所需的物理模型,以再现受应力作用下的先进FinFET行为。 该仿真器配置包括:Masetti掺杂依赖迁移率、Canali速度饱和模型、IALMob模型、压阻迁移率、Shockley–Read–Hall (SRH) 复合、奥格复合、带间隧穿、变形势理论、态密度修正以及密度梯度量子修正。

该模型堆栈反映了目标问题并非经典的长沟道MOSFET这一事实。 在7纳米级FinFET工艺节点上,亚阈值静电效应、迁移率退化、量子限制效应以及应力敏感输运现象均至关重要,且它们在三维几何结构中相互作用。基于变形势的物理模型和压阻式迁移率校正尤为重要,因为正是这些机制将机械应力转化为电学效应。

纳入这些模型并非仅仅为了追求完整性。之所以需要它们,是因为目标问题本质上对布局敏感。简化的仿真器虽然可能再现晶体管的标称行为,却完全忽略了局部几何结构变化时所产生的敏感性。完整的模型堆栈使该框架能够对它试图解释的那些效应做出响应。

6. 为什么应力张量分解才是真正的关键?

整个框架的核心在于一个观点:并非所有应力都是一样的。仅凭单一的标量应力值不足以解释现代FinFET器件的实际行为,尤其是当n型和p型器件的测量灵敏度存在显著差异时。因此,该分析将应力场分解为主要分量——特别是纵向、垂直和横向应力,并研究了它们各自如何影响电学响应。

正是这种分解使PMOS与NMOS之间的非对称性在物理层面上得以理解。结果表明,纵向应力是导致p型器件布局敏感性的主要因素,这解释了为何PMOS器件会对扩散断裂和栅极切割配置表现出如此强烈的依赖性。对于n型器件,情况则更为复杂:垂直和横向应力分量可能变得更为重要,且由于多个分量之间存在部分竞争,其净电学响应通常较小且不那么单调。

这是整个建模工作中最有趣的发现之一。PMOS 更强的灵敏度不仅仅是一种基于测量数据的经验观察;它已成为不同载流子在三维器件结构内对不同应力取向作出响应时,所产生的、具有物理意义的后果。这正是 TCAD 能够提供的洞见,而仅凭测量数据则难以轻易揭示。

7. “硅谷验证”是如何证明该模型的可信度的?

一个TCAD框架只有在能够再现硅器件的实际行为时才具有意义。因此,我们对该3D模型进行了标定,并利用高密度测量数据集对其进行了验证,特别关注了与应力相关LLEs最相关的布局场景。对于PMOS和NMOS器件而言,仿真结果与测量结果均表现出高度一致,且该框架成功再现了与扩散中断和栅极切断敏感度相关的主要趋势。

这一验证步骤尤为重要,因为目标效应并不总是很显著。在某些情况下,偏移量仅为几个百分点,尤其是对于n型器件而言。因此,能够同时再现PMOS器件较大的灵敏度以及NMOS器件较小且更复杂的响应,是对模型可信度的一次有意义的检验。这表明该框架不仅适用于拟合单个标准器件,还能准确捕捉不同器件极性和配置下与布局相关的物理特性。

正是这种验证,使得该框架后来能够应用于更广泛的工艺研究。一旦模型被证明能够再现测得的布局敏感性,便可进一步探索诸如栅极切割时序、介电隔离材料的选择、SDB沟槽宽度、间隔层厚度以及温度等因素——若仅通过实验,要对所有这些组合进行独立验证将困难得多。

8. 应力物理学如何转化为紧致模型?

该框架最具价值的特点之一在于,它不仅限于应力仿真。提取出的灵敏度被明确映射到与BSIM-CMG相关的紧凑模型参数中,包括U0、UA、DVTP0、DVTP1、DVTP2和LPE0。这一步至关重要,因为它将物理研究转化为能够直接影响电路仿真和设计流程的内容。

正是这种映射关系,让这项工作的广泛重要性显得尤为突出。 如果这些成果仅局限于TCAD领域,虽然有助于理解器件物理特性,但对设计支持的作用将大打折扣。通过将应力诱导的布局敏感性与紧凑模型参数建立联系,该框架开辟了一条从布局敏感的器件行为到SPICE兼容电路影响的通路。这种桥梁正是PDK开发、DTCO、变异性感知仿真以及良率导向设计分析所必需的。

这进一步印证了整个系列的核心观点之一:在高级节点中,布局不仅仅是一种绘图产物。它是一种物理边界条件,最终必须体现在模型设计师日常使用的模型中。而紧凑模型映射正是实现这一目标的关键。

9. 该框架释放了哪些新功能?

经过校准和验证后,该框架已不仅仅是一个器件仿真器。它成为了一种提出“如果……会怎样?”这类问题的方法,而这些问题对先进工艺节点的技术开发具有直接影响。 该模型被用于评估栅极切割策略、间隙层沉积方案、介质隔离材料、SDB沟槽宽度变化、间隙层厚度波动以及温度等因素的影响,揭示了这些工艺或布局参数如何改变应力相关LLE行为的幅度,有时甚至会改变其极性。

其中一些结果尤为引人注目。分析表明,栅极刻蚀时序会显著影响应力敏感性;介电隔离材料可大幅提升或降低PMOS器件的性能;SDB过蚀对PMOS器件的负面影响远大于NMOS器件;而温度从300 K升至375 K,会使n型器件的LLE敏感性降低约80%,p型器件则降低约40%。 这些并非抽象的观察结果;它们展示了该框架如何指导工艺和集成开发中的实际权衡决策。

这是该模型最具实际意义的方面之一。它将测得的硅材料变异性转化为可付诸实践的工艺洞见,这正是TCAD在工业半导体领域所能提供的最直观的价值体现之一。

10. 当前框架存在哪些固有局限?

一个可靠的建模框架不仅要明确其能做什么,还要明确其不能做什么。该模型并不试图模拟完整的晶圆级变异性,且其中部分工艺假设仍受限于底层技术的专有性质。 该模型的重点在于局部工艺波动、局部几何形状扰动以及与应力相关的电学敏感性,而非试图再现整个晶圆厂环境中所有可能的制造变异源。

此外,该框架还存在与节点和代工厂可移植性、测量噪声、简化应力表征、静态几何假设以及计算成本相关的局限性。这些并非次要的注意事项。它们界定了该框架的实际适用范围,并明确指出应将其视为一种功能强大但存在局限的工程工具。它能够解释和预测一大类与布局相关的效应,但并不能完全替代硅片表征或全面的制造变异性分析。

实际上,这正是该框架的优势之一。该框架目标远大却不流于空泛。它针对一个具体问题——先进FinFET器件中的应力相关局部布局效应——而设计,并以一种既符合物理原理又具有实际应用价值的方式解决了这一问题。

结论

如果上一篇文章介绍了如何测量与应力相关的局部布局效应,那么本文将探讨如何将这些测量结果转化为具有预测能力的物理模型。 一个有用的局部布局效应(LLE)模型不仅要拟合电学曲线,还必须在一个既符合物理原理又经过实验验证的框架内,将局部几何结构、工艺诱导应力、各向异性载流子输运以及测得的器件响应联系起来。这正是3D TCAD流程构建的初衷。

通过结合工艺感知型3D FinFET结构、两阶段校准流程、丰富的输运与应力物理模型堆栈,以及基于高密度硅片测量数据的验证,该框架为理解商用7nm FinFET工艺中的布局相关变异性提供了预测依据。 该框架还架起了器件级应力物理与紧凑模型参数之间的桥梁,使其研究成果直接适用于PDK开发、DTCO、工艺优化以及考虑变异性的设计。

一旦有了这样的模型,接下来最有趣的问题便是:硅元素究竟揭示了关于最强LLE机制的哪些信息?讨论自然会转向这一方面。

接下来会发生什么

在下一篇文章中,我们将从建模框架转向主要研究结果:扩散断裂、栅极切割、多级间距和鳍间距如何影响已测量的7nm FinFET结构的电学行为;为何PMOS器件比NMOS器件敏感得多;以及结合测量与TCAD分析的结果揭示了哪些关于底层应力物理机制的真相。