このシリーズの最初の記事では、核心となる問題について紹介しました。すなわち、先進的なCMOS技術においては、トランジスタの挙動はもはや公称寸法だけで決まるものではないということです。周囲のレイアウトも重要な要素となります。 隣接する構造、局所的な形状、およびプロセスに依存する応力場は、いずれもチャネルに外乱を与え、局所レイアウト効果(LLE)として知られる系統的なばらつきを引き起こす可能性があります。現代のFinFETノードにおいて、これらの効果は、ばらつき、コンパクトモデリング、DTCO、および歩留まりを考慮した設計において重要な要素となっています。

そこで当然、より難しい疑問が浮かび上がります。シリコン上のLLEを実際にどのように測定すればよいのでしょうか?2つのトランジスタの電気的特性に違いがある場合、その原因が局所的な応力なのか、ゲートエッジの近接効果なのか、寄生抵抗なのか、プロセスばらつきなのか、あるいは単なる測定ノイズなのか、どうすれば判別できるのでしょうか?言い換えれば、先進的なプロセスノード内で発生している他のあらゆる要因と混同することなく、レイアウト環境の影響をどのように切り分けることができるのでしょうか?

その答えは、実験計画法から始まります。本研究では、市販の7nm FinFETプロセスで製造された高密度特性評価チップを利用しており、3万個以上の被測定デバイス(DUT)が搭載されています。これらのデバイスは、レイアウトに依存する特定のメカニズムを分離するように設計された、綿密に構成されたモジュール内に配置されています。 全体的な手法としては、実験計画法(DOE)戦略、レイアウト制御されたテスト構造、自動化された電気的特性評価、および統計的に堅牢なデータ解析を組み合わせています。その目的は、単に多数のデバイスを測定することではなく、個々のLLE(レイアウト依存効果)の寄与を分離し、後でモデル化や予測が可能にすることにあります。

本稿では、その実験手法に焦点を当てます。具体的には、チップの構成、特定の電気的観測量が選ばれた理由、DOE(設計オペレーター)の構築方法、そしてレイアウトに起因する実際の挙動とバックグラウンドの変動を分離するために測定フローがどのように構成されたかについて解説します。

1. なぜ変動要因を特定するのはそれほど難しいのか?

先進ノードにおけるトランジスタのばらつきは、決して単一のメカニズムによって引き起こされるものではないため、局所的なレイアウト効果を実験的に研究することは困難である。 実際のFinFET技術においては、電気的特性は、応力、リソグラフィー相互作用、局所的なパターン密度、ウェル近接、ドーピングに関連する擾乱、仕事関数の変動、寄生抵抗、およびより広範なプロセス変動などの影響を受ける可能性がある。拡散ブレーク近接やゲートカット配置といった特定の効果を分離することが目的であるならば、実験フローは、レイアウトに依存する寄与が他の要因に埋もれることなく明確に現れるように構築されなければならない。

そのため、測定戦略は「制御された差異化」に基づいています。つまり、レイアウトの属性を一度に一つずつ変化させ、周囲の条件を可能な限り安定させ、チップ全体で構造を再現し、統計的な集計を用いて体系的な傾向を明らかにするのです。その目的は、単にばらつきを観察することではなく、それを分解することにあります。

これは、応力に関連するLLEsにおいて特に重要です。機械的応力は、電気的測定では直接確認することができません。制御された再現性のある方法で局所的な形状を変化させた際に、デバイスのパラメータがどのように変化するかから推測する必要があります。そのため、実験設計は電気的測定そのものと同じくらい重要となります。

2. 特定の効果を分離するために、テスト用チップはどのように構築されたのか?

この特性評価プラットフォームは、市販の7nm FinFET技術で実装された高密度テストチップであり、専用の構造体全体に3万個以上のDUTが配置されています。この規模は重要です。微細ながらも体系的なレイアウトの影響を特定することが目的であるならば、わずかな数のデバイスでは不十分です。 複数のレイアウト環境を比較するための十分な再現性、有意義な局所環境を維持するための十分な制御、そして決定論的な挙動とランダムなばらつきを区別するための十分な統計的深みが必要です。

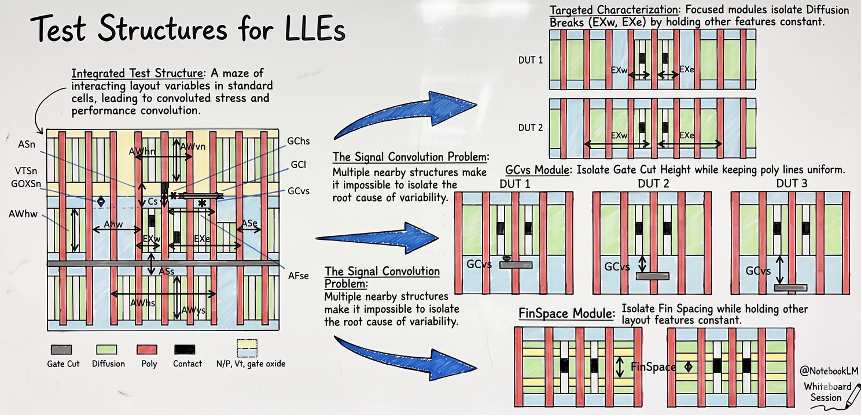

そこで、このチップはモジュール式の特性評価戦略を用いて設計された。あらゆる変動要因を一度に測定しようとするのではなく、レイアウトを特定のLLEカテゴリを対象とした専用ブロックに分割した。 拡散遮断(Diffusion Break)近接効果、ゲートカット近接効果、ウェルまたはp–n境界効果、フィンピッチ、ポリピッチを調査するために、個別のモジュールが構築された。このモジュール性は、より複雑な相互作用を検討する前に、各メカニズムを比較的独立して検証できるため、本手法の最大の特徴の一つである。

被試験デバイス(DUT)周辺の局所環境は、構造間の比較が有意義なものとなるよう、厳密に制御された。その目的は、任意の製品レイアウトを模倣することではなく、単一の幾何学的パラメータを変化させ、その電気的挙動を観察できる、代表性があり再現性のある局所環境を作り出すことにあった。この原則こそが、本手法全体の核心をなしている。

3. 実験計画法(DOE)の役割とは何か?

測定フローの中核となるのは、レイアウトを考慮した実験計画法(DOE)である。その基本原則は単純明快である。特定のレイアウト特性がトランジスタの挙動に影響を与えると疑われる場合、その特性を制御された方法で変化させつつ、その周辺環境は可能な限り一定に保つ必要がある。実際には、これは、ある幾何学的パラメータのみを変更し、周囲の条件は固定したままにする構造群を設計することを意味する。

このアプローチを用いて、レイアウトに依存する主要なメカニズムを、より小さく扱いやすい部分問題に分割した。拡散遮断部やゲートカット付近に配置した場合、あるいは異なるフィンピッチやポリピッチ条件下でデバイスがどのように応答するかを調査するために、専用のモジュールが作成された。 対象となる特徴が1つだけ異なるDUTを比較することで、この手法により、電流、しきい値電圧、またはサブスレッショルド挙動の変化を、制御不能なバックグラウンド変動ではなく、特定の幾何学的要因に起因するものとして特定することが可能になります。

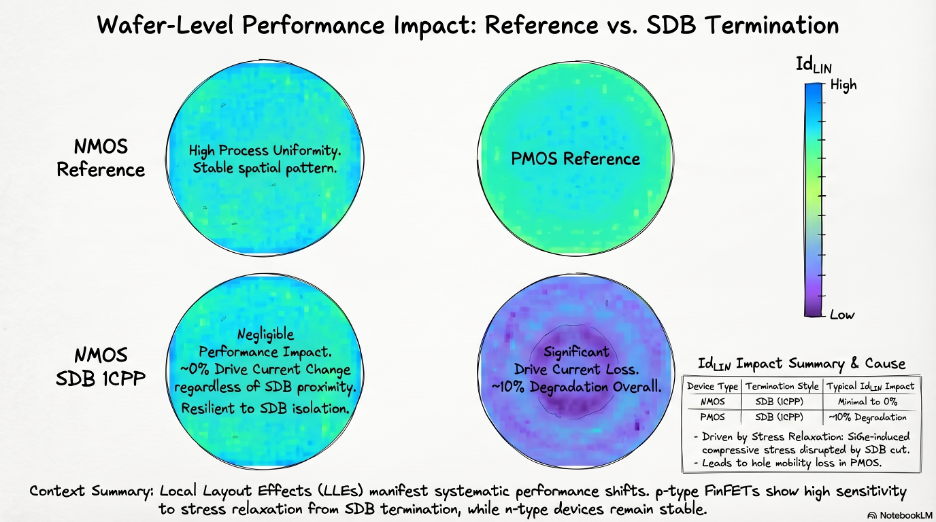

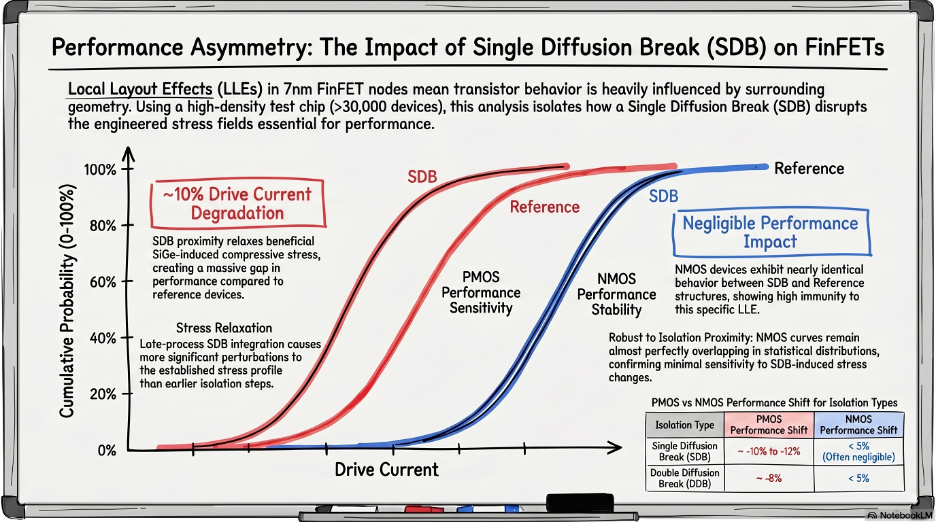

再現性は当初から組み込まれていた。デバイス種別やしきい電圧の特性にかかわらず、同じ設計思想が貫かれていたため、効果の有無を特定できるだけでなく、それがデバイスの極性や動作条件にどの程度依存するかを理解することも可能となった。これが、p型デバイスがn型デバイスに比べて、ストレスに関連するレイアウトの乱れに対して著しく敏感であることをデータが明確に示している理由の一つである。

4. なぜ線形領域電流が最適な応力モニターなのか?

応力に関連する変動を監視することを目的とする場合、すべてのトランジスタパラメータが等しく有用であるとは限らない。 特に線形領域において、Id-Vgd測定から得られる電気的量に重点が置かれた。この選択には物理的な根拠がある。すなわち、キャリア移動度は機械的応力に対して非常に敏感であり、線形領域では、速度飽和やその他の非線形効果がより大きな役割を果たす深飽和領域に比べ、ドレイン電流が移動度に関連する変化をより直接的かつ解析的に把握しやすい指標となるからである。

こうした理由から、線形領域のドレイン電流が応力モニタリングの主要な観測量の一つとして採用された。これは、物理的な解釈可能性、寄生要素への感度の低減、および測定の安定性という要素の間で、有益なバランスを提供する。実用的な観点からは、これは電気的データと、局所的な応力や移動度の乱れに基づくその後の物理的解釈とを結びつける実験的な架け橋となる。

とはいえ、特性評価の流れでは、より広範なパラメータセットが使用されている。測定は線形領域と飽和領域の両方で行われ、抽出された指標にはIoff、Ion、Vt、サブスレッショルド・スイング、およびその他の電流や抵抗に関連する量が含まれていた。LLEメカニズムのすべてが同じように現れるわけではないため、この豊富なパラメータセットは重要である。すなわち、移動度を主に乱すものもあれば、しきい電圧をシフトさせるもの、あるいは寄生特性やショートチャネル挙動をより間接的に変化させるものもあるからだ。

5. テスト構造も重要:なぜPMAが最適な選択だったのか?

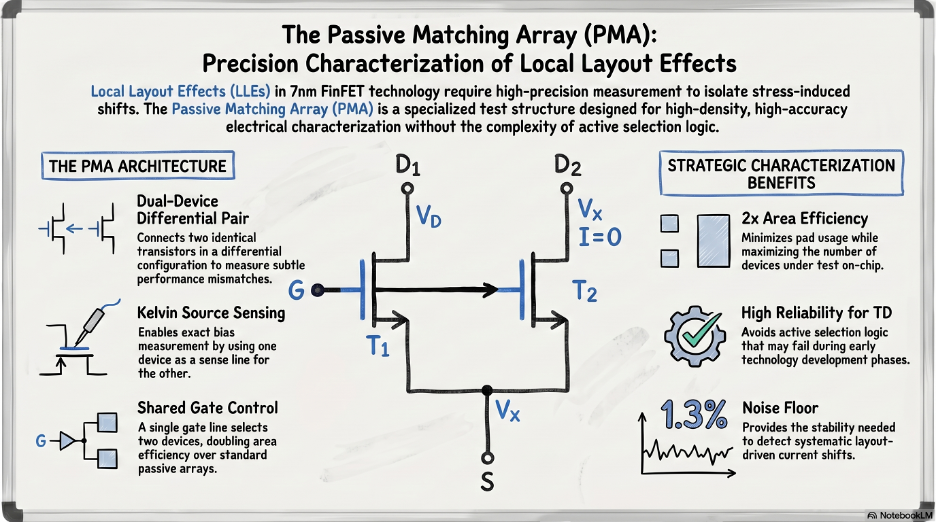

この手法は、デバイスのレイアウトだけでなく、デバイスへのアクセスに用いられる測定構造の設計にも依存する。シングル・パッテッド構造、パッシブ・アレイ、アクティブ・アレイ、パッシブ・マッチング・アレイ(PMA)など、いくつかの形態のテスト・インフラストラクチャが評価された。これらの中で、PMAは面積効率、測定精度、信頼性の点で最適なバランスを提供していたため、最適なソリューションとして採用された。

この選択は、一見した以上に重要です。先進ノードの特性評価において、テストに用いる構造そのものが手法の一部となります。面積を過度に消費する構造は、チップ上に配置できる有用な複製数を減少させます。電気的ノイズの多い構造は、結果の統計的品質を低下させます。 制御された局所環境(LLE)を維持できない構造では、観測されたシフトを特定のLLEメカニズムに帰属させることが困難になります。PMAが選ばれたのは、異なるレイアウト環境に配置された、名目上類似したデバイス間において、より堅牢かつスケーラブルな比較を可能にするためです。

PMAフレームワークは比較測定も可能にし、これはLLE解析において特に有用です。これらの影響は、1つのDUTを、レイアウト上の1つの特徴のみが異なるほぼ同一の参照サンプルと直接比較することで、より容易に特定できることがよくあります。この比較の考え方は、手法全体を通じて貫かれています。

6. なぜ自動化された高速特性評価が不可欠だったのか?

チップとDOEが定義されると、新たな課題として「スケール」が浮上します。3万個以上のデバイスを搭載したテストチップを、手動のワークフローでは効率的に特性評価することはできません。そのため、今回の測定プロジェクトでは、電気的データの取得にpdFasTest®、データの自動取り込みと分析にExensio®といった産業用インフラを活用し、自動化された高速パラメトリックテストを実施しました。これにより、特性評価フローは個別の測定から、構造化され再現性のあるデータパイプラインへと移行しました。

測定は、線形領域および飽和領域の両方で収集されたId-Vgsスイープに基づいて行われ、そこから主要な電気的パラメータが抽出された。 その後、解析フローにおいて測定結果をレイアウト記述子および空間情報と統合し、CDF、ウェーハマップ、およびパラメータレポートを生成しました。これは、LLE特性評価では常に「局所的な幾何学的影響は何か」という問いと、「その影響が、より広範なウェーハレベルやプロセスレベルのばらつきと比較してどの程度の大きさか」という2つの問いに同時に答えなければならないため、重要なことです。

自動抽出により、数千もの関連構造を一貫した方法で評価することも可能になった。研究対象となる影響の大きさがわずか数パーセントに過ぎない場合、こうした一貫性は極めて重要となる。取得と報告の標準化がなければ、わずかな傾向が物理的に意味のあるものなのか、それとも単に分析方法の不統一によるものなのかを見極めるのは、はるかに困難になるだろう。

7. 統計的な頑健性はどのように保証されたのか?

この手法の最大の特徴の一つは、統計的な頑健性を重視して構築されている点である。デバイスパラメータは中央値を用いて分析され、実験全体を通じて、ドレイン電流の観測された標準偏差は約1.3%未満、しきい値電圧およびサブスレッショルド・スイングの標準偏差は約1.6%未満に抑えられた。これらの数値は、系統的なLLEシフトを検出する際の基準となるバックグラウンドノイズフロアを定義するものであるため、極めて重要である。

これが、レイアウトに起因する影響が数パーセント、さらには特定のレイアウト構造の近傍にあるp型デバイスでは10パーセントを超えるという、信頼性の高い主張が可能になる理由の一つである。バックグラウンドのばらつきが定量化され、制御されれば、観測されたシフトは単なる偶発的なばらつきではなく、物理的な信号として解釈できるようになる。この手法の強みは、単に多くのデバイスを測定することにあるだけでなく、統計的に厳密な方法で測定することにある。

中央値、再現性、および制御された比較を重視するこのアプローチは、その後のモデリング作業においても重要である。予測を行うTCADやコンパクトモデル・フレームワークの精度は、その較正に用いられるデータの質に左右される。実験のベースラインデータにノイズが多く含まれていたり、構造が不十分であったりする場合、モデルは一見適合しているように見えても、物理的な妥当性を欠く可能性がある。今回の測定手法は、まさにその落とし穴を回避するために明確に設計されたものである。

8. 測定結果は物理的解釈にどのように寄与するのか?

この手法の大きな強みは、電気的観測にとどまらない点にある。特性評価フロー全体は、当初から物理的な解釈やその後のモデル校正を支援できるよう設計されている。そのため、試験用構造体は、電気的読み取りのしやすさだけでなく、3D TCAD ベースの応力シミュレーションとの互換性も考慮して選定された。実験側とモデリング側は、互いに補完し合うように構築されている。

この点が核心です。純粋に実証的な測定調査では、あるレイアウトが別のレイアウトよりも優れているか劣っているかは分かりますが、必ずしも なぜか。対照的に、本研究の手法は、シリコン上で観測された電気的傾向を、応力テンソルの成分、移動度の摂動、幾何学に依存するプロセス間の相互作用といった物理的に意味のある変数へと結びつけられるように構築された。それこそが、後に観測の域を超え、予測へと進むことを可能にする所以である。

だからこそ、主要な特性評価の対象、特に「ディフュージョン・ブレイク」や「ゲート・カット」といった効果については、慎重に選定されたのです。これらは決して恣意的に選ばれたレイアウトの特徴ではありません。これらはまさに、先進的なFinFET集積技術において局所的な応力境界条件を変化させる構造であり、それゆえに、レイアウト、プロセス、そして測定可能な電気的挙動の間に直接的な関連性を築くものなのです。

9. この実験手法は最終的に何を実現したのか?

この実験的フレームワークは、最終的にいくつかの重要な成果をもたらしました。第一に、シリコン上の個々のLLEの寄与を体系的に分離する方法を提供しました。第二に、3D TCADのキャリブレーションと検証を支えるのに十分な信頼性を持つデータを生成しました。第三に、PDK開発、DTCO、およびプロセス最適化に直接関連する、レイアウト形状から電気的感度への実用的な道筋を確立しました。

これが、このアプローチ全体において最も価値のある点の一つです。すなわち、この方法論は学術的に厳密であるだけでなく、産業的にも有用であるということです。この方法論は、実際の技術開発プロセスにおいて重要な疑問に答えるよう設計されています。具体的には、どのようなレイアウトの特徴が有害な応力変動を引き起こすのか、どのデバイスが最も影響を受けやすいのか、その変動の程度はどの程度なのか、製品設計が確定する前にその挙動を予測できるのか、そしてそれらの予測を、設計者や技術者にとって実践的な指針へと変換できるのか、といった点です。

その意味で、特性評価の手法は単なる実験の基盤にとどまらず、その後のモデリングや解釈に信頼性をもたらすものです。シリコン上でLLEを確実に特定する確固たる方法がない限り、予測モデリングの試みはあくまで推測の域を出ないでしょう。

結論

このシリーズの第1回が、応力に関連する局所レイアウト効果(LLE)がなぜ重要なのかについて述べたものだったのに対し、第2回となる今回は、それらをどのようにして有意義な方法で測定できるかについて解説します。 重要なポイントは、先進的なFinFETノードにおけるLLEの特性評価は、その場限りのトランジスタ測定に頼ることはできないということです。これには、専用の実験アーキテクチャが必要です。具体的には、大規模かつ綿密に設計されたテストチップ、レイアウトの特徴を1つずつ変化させる実験計画法(DOE)、堅牢な電気的観測項目、自動解析、そして真の系統的効果とバックグラウンドのばらつきを区別するための十分な統計的厳密性が求められます。

3万個を超えるDUT、モジュールレイアウトを考慮した構造、高速パラメトリックテスト、および統計的に管理されたデータ抽出を組み合わせることで、7nm FinFET技術における応力関連のLLEsを理解するための強固な基盤が構築されます。

こうした実験的基盤が整えば、次の問いは必然的に浮上します。すなわち、これらのシリコンに関する観測結果を、いかにして物理的かつ予測可能なモデルへと変換するか、ということです。そこで登場するのがTCADです。

次は何が待っているのか

次回の記事では、実験による特性評価からモデル構築へと話を進めます。具体的には、測定された挙動を再現するために3D TCADフレームワークがどのように構築・調整されたか、局所応力テンソルがどのように抽出されたか、そしてレイアウトに起因する応力の電気的影響がどのように予測モデリングフローに組み込まれたかについて解説します。