数十年にわたり、CMOS技術の進歩は、2つの極めて強力な概念によって牽引されてきた。ムーアの法則はトランジスタ密度の指数関数的増加を捉えたものであり、一方、デナードのスケーリング則は、トランジスタの微細化によって、性能の向上、消費電力の低減、および面積の縮小が同時に実現できる理由を説明した。その歴史的な時代において、スケーリングは、ほぼ「コストをかけずに」これらの利点を稀に見るほどに組み合わせたものをもたらした。

その時代はすでに過去のものとなった。CMOSがナノスケールの深層時代に入ると、従来の電力・性能・面積(PPA)の向上を保証するには、微細化だけでは不十分になった。物理的な微細化は続いたものの、その効果は次第に薄れ、進歩はアーキテクチャの革新、プロセスの統合、そして設計と技術の共同最適化(DTCO)にますます依存するようになった。言い換えれば、トランジスタの挙動は、もはやデバイスの公称寸法だけでは理解できなくなったのである。

この変化がもたらした最も重要な結果の一つは、周囲のレイアウト自体がデバイスの構成要素となったことです。高度なFinFET技術においては、トランジスタ周辺の局所的な幾何学的環境が、応力、静電効果、およびプロセスに依存する相互作用を通じて、その電気的挙動に測定可能な変化をもたらす可能性があります。こうした影響の中でも、応力に関連する局所レイアウト効果(LLE)は、体系的なばらつきの特に重要な要因として浮上しています。

このトピックは、本博士課程研究の焦点であり、実験とモデリングを組み合わせた枠組みを用いて、市販の7nm FinFET技術における応力誘起型LLEs(線形性逸脱)を調査するものである。本研究は、3万個以上のデバイスを搭載した高密度テストチップ、レイアウト依存の影響を分離するための専用の実験計画法(DOE)、およびシリコン測定値に基づいて校正された3D TCADフローに基づいている。 p型デバイスにおいて、一部のレイアウト依存性の応力変動が10%を超える性能変動を引き起こすことが判明しており、これは先進ノードにおいて局所的な形状がトランジスタの挙動にどれほど強い影響を及ぼし得るかを浮き彫りにしている。

この最初の記事では、本シリーズの概要を説明します。ストレス関連LLEsがなぜこれほど重要になったのか、それらが「ハッピー・スケーリング」の終焉とどのように関連しているのか、そしてなぜ現在、デバイス物理学、コンパクトモデリング、DTCO、および歩留まりを考慮した設計の交差点に位置しているのかを解説します。続く記事では、測定手法、モデリングの枠組み、シリコン実験の主な結果、そして将来のFinFETおよびGAA技術への示唆について、さらに深く掘り下げていきます。

1. なぜ「ハッピー・スケーリング」は厳しい現実に取って代わられたのか?

CMOS微細化がもたらした歴史的な展望は、シンプルかつ強力なものでした。すなわち、トランジスタを小型化すれば、回路は高集積化され、高速化され、エネルギー効率も向上するというものです。理想的なデナードの法則に基づく微細化では、0.7倍という代表的な線形縮小率により、トランジスタ面積は約半分に縮小されると同時に、遅延時間が短縮され、動的消費電力も低減されました。この相乗効果が、技術微細化に関する従来のPPA(性能・電力・面積)観の基盤となったのです。

しかし、トランジスタの微細化がナノスケールの深層領域へと進むにつれ、この有利な状況は徐々に弱まっていった。ショートチャネル効果、リーク電流、および電源電圧の制約が支配的になると、微細化のみではそれ以上の性能向上を引き出すことができなくなった。その時点で、さらなる進歩は、プロセス技術の向上、新素材、より複雑なデバイス構造、そして技術と設計の間のますます積極的な共同最適化に大きく依存するようになった。

この変化は、単なる歴史の脚注に過ぎないわけではない。かつては二次的なものとされていた変動メカニズムが、今や中心的な役割を担うようになった理由を説明している。マージンが厳しくなり、デバイス構造が3次元化し、レイアウトの集積化が急速に進む世界では、一見些細な幾何学的詳細が、測定可能な電気的差異へと波及し得る。まさにそのような環境において、局所的なレイアウト効果が極めて重要となるのである。

2. なぜ先進プロセスでは機械的応力がそれほど重要なのか?

機械的応力は、長年にわたり、最先端CMOS技術において最も有用かつ繊細な物理的制御手段の一つとされてきた。ひずみ制御に関連する応力レベルにおいて、シリコンは弾性領域にとどまる。つまり、機械的変形は、恒久的な結晶学的損傷を引き起こすことなく、可逆的な方法で半導体のバンド構造を変化させる。これによる最も重要な電気的効果は、キャリア移動度の変化である。

この移動度応答は等方性ではない。シリコンにおいて、応力の影響は結晶方位、電流の方向、およびキャリアの種類に強く依存する。これは、先進的なFinFETロジック技術で広く使用されている(100)方位のウェハーにおいて特に重要である。電子と正孔は応力に対して同じように反応せず、この非対称性が、ひずみ制御がCMOSの最適化において極めて重要な手法となった理由の一つである。

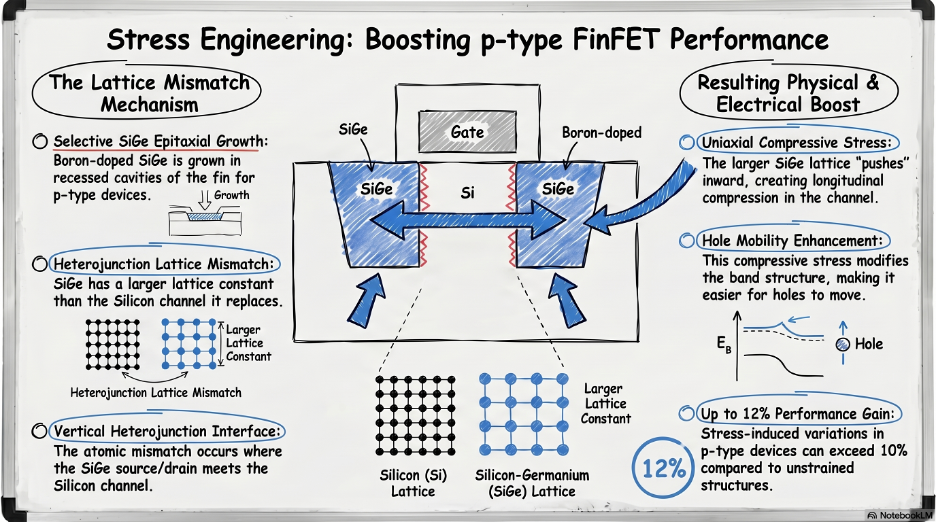

実際問題として、p型デバイスはn型デバイスよりも応力による移動度変化の影響を受けやすい傾向がある。この点は本論文においても核心的な要素となっている。シリコン測定およびTCAD解析の結果、p型FinFETは局所的な応力変動に対して著しく敏感であり、特定の構成ではレイアウトに依存して10%を超える変動が見られるのに対し、n型デバイスは通常、その応答が小さく、場合によってはより複雑な挙動を示すことが明らかになった。

つまり、ストレスは単なる身体的な背景要因にとどまらない。それはチャンスであると同時にリスクでもあり、可動性を高めるために意図的に活用できるツールである一方で、レイアウトの文脈と結びついた際には、望ましくない変動要因となる。

3. 設計されたひずみは、どのようにして予期せぬ応力へと変わるのか?

半導体業界では、長年にわたり意図的に応力を利用してきた。初期のひずみ制御技術では、ウェハーレベルでの格子不整合、例えば緩和されたSiGeバッファ上に成長させたシリコンなどを用いて、有益な全体的なひずみを誘起していた。これらの手法は平面技術や、その後のFD-SOIにおいて有効であったが、高度に三次元化されたアーキテクチャにおいては、その有効性が必ずしも明確ではなくなった。

非平面デバイスにおいてモビリティの向上を継続的に実現するため、業界はより局所的な応力制御技術に目を向けた。その例としては、埋め込み型エピタキシャル・ソース/ドレイン応力源、コンタクト・エッチング・ストップ層(CESL)、および応力記憶技術(SMT)などが挙げられる。これらの手法は、チャネルの局所的な機械的環境を意図的に改変するものであり、理想的なデナード則の限界を超えた後もCMOSの微細化を継続可能にした、幅広い技術手法の一部を成している。

しかし、応力がデバイスの最適化における重要な要素となると、避けられない疑問が生じます。それは、局所的なレイアウトによって意図せずその応力場が変化した場合、どうなるのか、ということです。ここで「局所レイアウト効果」が問題となります。設計者が意図的に追加の「応力要因」を導入していなくても、隣接するアクティブ領域、アイソレーション構造、ゲート終端、コンタクト配置、および局所的なパターン密度のすべてが、トランジスタのチャネルに作用する応力分布に影響を与える可能性があるのです。

「設計上のひずみ」と「レイアウトに起因する応力のばらつき」とのこの区別は極めて重要です。前者は意図的なものであり、設計上有益なものです。一方、後者は状況に依存し、直接視覚化することが困難な場合が多く、図面上の寸法が同一のトランジスタ間であっても、測定可能な個体差を生じさせる可能性があります。

4. ローカル・レイアウト効果(LLE)とは一体何なのか?

ローカル・レイアウト効果(LLE)とは、公称寸法のみではなく、周囲のレイアウト環境に起因して生じる、トランジスタの電気的挙動における体系的でパターン依存的な変動である。これらは、しきい値電圧、駆動電流、サブスレッショルド挙動などのパラメータに影響を及ぼす可能性がある。純粋にランダムな変動要因とは異なり、LLEは原則として決定論的である。つまり、LLEは単なる「ノイズ」ではなく、その基礎となる物理的メカニズムやプロセス依存性を十分に理解していれば、特性評価やモデル化が可能な現象である。

先進的なFinFET技術において、いくつかの種類のレイアウト要素がLLE(局所応力集中)の発生源となり得る。アクティブ領域の形状や近隣構造物との近接性は、局所的な応力分布を変化させる可能性がある。ゲートの終端や配線の終端位置は、静電的挙動と機械的境界条件の両方に影響を及ぼす。ウェルエッジへの近接は局所的なドーピング分布を乱す可能性があり、コンタクトの配置は寄生抵抗に影響を与えるだけでなく、近隣のプロセス起因の応力分布にも影響を及ぼす。

FinFETでは、チャネルが本質的に三次元構造であることに加え、ゲートスタック、ソース/ドレインの集積、スペーサー、および絶縁構造のすべてが密接に結合した機械的環境を形成するため、これらの相互作用は平面型デバイスに比べて著しく複雑になります。本論文では、最も詳細に調査された2つのLLEメカニズムとして、拡散遮断に関連する 効果とゲートカットに関連する効果が挙げられます。これらはいずれも、局所応力を変調させ、デバイス特性に著しい影響を及ぼすことが示されました。

だからこそ、LLEは単なるモデリング上の厄介事としてではなく、現代のデバイスアーキテクチャとプロセス集積化から生じる新たな特性として捉えるのが最も適切である。デバイスがより三次元化され、レイアウトがよりコンパクトになるにつれ、トランジスタはその周辺環境の影響をますます強く「感じる」ようになる。

5. なぜDTCOはLLEの重要性を高めるのか、むしろ低下させるのではなく?

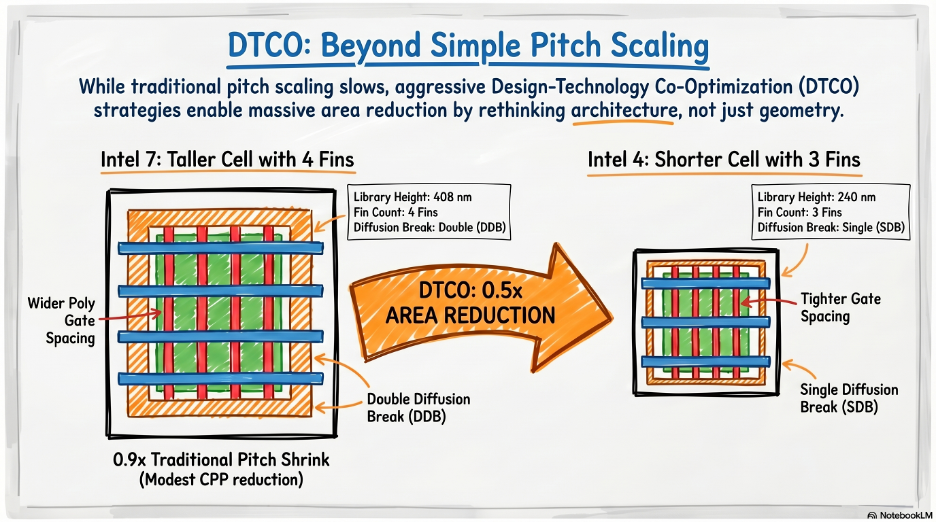

ピッチの微細化だけでは密度向上が限界に達した現在、設計技術の協調最適化(DTCO)は、密度向上を持続させるための主要な手法の一つとなっています。現代のプロセスノードでは、コンタクト間ポリシリコンピッチ、フィンピッチ、あるいはメタルピッチの微細化だけに頼るのではなく、セルアーキテクチャ、トランジスタ配置、配線リソース、および設計ルールを包括的に見直すことで、面積削減を実現する傾向が強まっています。

代表的な例として、Intel 7からIntel 4への移行が挙げられる。この移行では、密度の向上はピッチの縮小だけでは説明がつかなかった。インテルは、物理的な微細化に加え、スタンダードセルの高さの低減、フィンの密度低減、拡散層間の間隔の縮小といったDTCO(設計・技術・プロセス・アーキテクチャ)主導の変更を組み合わせることで、現代の集積密度の進歩がジオメトリとアーキテクチャの両方によってもたらされることを示した。

しかし、こうした戦略はレイアウト依存性を悪化させる要因にもなります。ディフュージョン・ブレイク、ゲートカット、アイソレーションエッジ、その他の隣接する構造がアクティブチャネルに近づくにつれて、それらの機械的および電気的な影響は強まります。かつては比較的安全な距離に配置されていた構造も、今ではトランジスタの有効な相互作用領域内に収まってしまうのです。言い換えれば、面積スケーリングの回復に寄与する技術そのものが、LLEを増幅させる要因にもなり得るのです。

これが本論文の重要なメッセージの一つである。すなわち、DTCOとLLEの感度は密接に関連しているということだ。局所的な形状が応力にどのような影響を与えるかを理解せずに、レイアウトのコンパクト化を強引に進めると、その代償として、原因不明のばらつき、マッチングの劣化、あるいは設計マージンの縮小といった問題が後々現れる可能性がある。したがって、応力を考慮したDTCOと、LLEを考慮したコンパクトモデリングは、単なるオプション的な改良ではなく、先進ノード開発において不可欠な要素となる。

6. FinFETは、ある問題を解決した一方で、別の問題を露呈させてしまったのはなぜか?

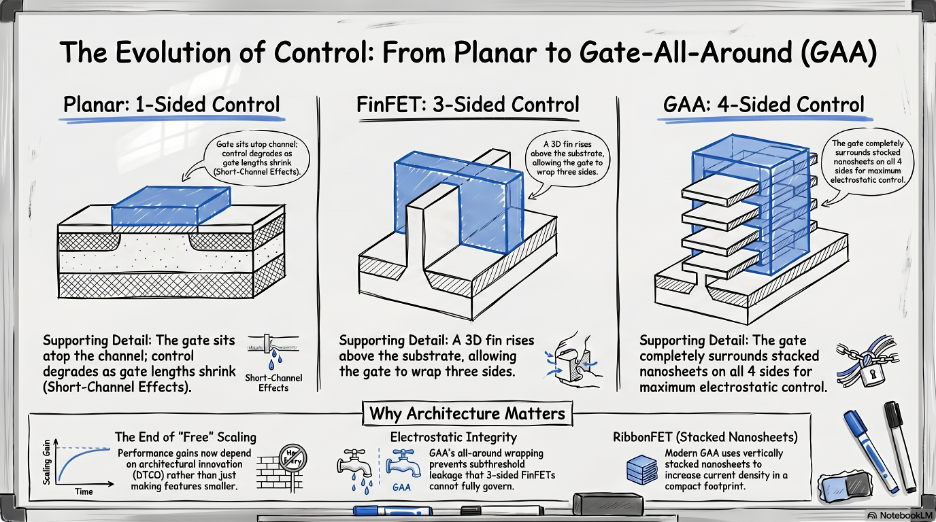

平面型MOSFETからFinFETへの移行は、微細化がナノメートル領域へと進むにつれ、静電制御機能を回復させる必要性から推進された。マルチゲート構造は、平面型デバイスよりもチャネルに対する制御性を大幅に高め、リーク電流を低減させるとともに、CMOSの微細化をさらに1世代分延長させた。

しかし、FinFETへの移行に伴い、機械的な環境もはるかに複雑なものとなった。フィンの形状、ゲートスタック、絶縁層、ソース/ドレインの応力要因、そして局所的なパターン密度が相まって、平面型デバイスに比べて理解も抽象化もはるかに困難な三次元の応力分布が生み出される。したがって、静電特性を改善したこのアーキテクチャの転換は、応力に関連するレイアウトの影響を構造的により重要なものにしたのである。

今後、業界はナノシートデバイスなどのゲート・オール・アラウンド(GAA)アーキテクチャへと移行しつつある。GAA構造は、チャネルを四方からゲート材料で囲むことで静電制御をさらに向上させ、水平方向のフィン増設を続けるのではなく、チャネルの垂直積層によって微細化を実現する。インテルのRibbonFETや、他社による同様のGAAアプローチは、この移行を反映している。

同時に、裏面給電(例えば 、インテルの18Aプロセスにおける「PowerVia」 ) といった先進的な相互接続技術の革新により、トランジスタ周辺のレイアウトや配線環境が変化しつつある。 これと並行して、高NA EUVは、単一露光での解像度とオーバーレイ性能を向上させることでパターニング能力を拡大しており、ASMLは0.55-NAシステムで8nmの解像度を達成したと報告し、imec/ASMLは1回の露光で20nm未満のピッチでのパターニングを実証しています。これらの進歩により、さらなる集積密度の向上が可能になりますが、同時に、パターンの忠実度、プロセス制御、およびレイアウトを考慮したばらつきの管理が、これまで以上に重要になっていきます。

つまり、デバイスのアーキテクチャは進化しているものの、そこから得られる核心的な教訓は変わらない。すなわち、スケーリングがより三次元的になり、相互最適化が進むにつれて、局所的なコンテキストの重要性は高まるということだ。むしろ、GAA時代において、この問題は単純化するどころか、より複雑化していると言えるだろう。

7. なぜ予測モデリングはもはや必須となったのか?

LLEが、デバイスの電流やしきい値電圧、ひいては回路のタイミングや消費電力に影響を与えるほど大きくなれば、シミュレーション上で表現されなければなりません。つまり、その影響はプロセスの直感や製造後のデバッグの範囲内に留めておくことはできず、SPICE互換のコンパクトモデルや、ばらつきを考慮した設計フローへと変換する必要があるのです。

応力に関連するLLEsを予測するためのフレームワークには、密接に関連したいくつかのステップが必要です。まず、エピタキシャル領域、ゲート材料、STI、CESLなどの関連するひずみ源について、応力テンソルの完全な解像度と現実的な仮定を用いた、プロセスを意識した機械的シミュレーションを通じて、局所的な応力場を抽出する必要があります。次に、その応力情報を、ウェハーの配向、電流の方向、キャリア種、デバイスアーキテクチャを考慮した圧電抵抗型移動度モデルを通じて、電気的影響に変換する必要があります。 第三に、これらの物理的感度を、設計者が回路レベルで実際に使用できる、レイアウトを考慮したコンパクトモデルパラメータへと抽象化する必要がある。最後に、個々のレイアウト効果を分離するように特別に設計されたシリコン測定結果を用いて、フレームワーク全体を検証しなければならない。

本論文では、まさにこの方向性を追求している。本研究では、高密度7nm FinFETテストチップに対する体系的な測定と、校正済みの3D TCADフレームワークを組み合わせ、その結果得られた感度を、移動度やしきい値電圧のシフトといったコンパクトモデルに関連するパラメータにマッピングしている。 その目的は、観測された挙動を事後的に説明するだけでなく、DTCO、PDK開発、プロセスチューニング、および歩留まりを考慮した設計決定を支援できる予測手法を構築することにある。

レイアウトの微細化が進み、プロセスの複雑さが増すにつれ、こうしたモデルの重要性はますます高まっています。先進ノードにおいては、ばらつきの予測、設計の堅牢性、物理検証、そして市場投入までの期間短縮のため、LLEの正確な特性評価が不可欠になりつつあります。

8. 論文の根底にある核心的な主張

この研究全体を一言で要約するとすれば、次のようなものになるだろう:

先進的なFinFET技術において、レイアウトはもはやデバイスのマスクレベルでの記述にとどまらない。それはデバイスの物理的特性の一部となっている。

だからこそ、応力に関連するLLEs(微小電圧変動)は注目に値する。これらは、トランジスタのアーキテクチャ、プロセス集積化、機械的応力、コンパクトモデリング、そして回路レベルのばらつきを、一つの課題として結びつけている。また、これらは「ハッピー・スケーリング」の終焉が半導体工学の考え方をいかに変えたかを示す、最も明確な例の一つでもある。すなわち、性能の向上はもはや微細化によってのみもたらされるのではなく、かつては無視できるほど微小だった相互作用を理解し、制御することによってもたらされるのだ。

本研究では、シリコン特性評価、レイアウトを考慮した実験計画法(DOE)、応力シミュレーション、および電気的モデリングを組み合わせることでこの課題に取り組んでいる。特に、物理的に意味のある影響を特定し、それを実用的な設計・プロセス指針へと変換することに重点を置いている。こうした手法の組み合わせこそが、このテーマを特に興味深いものにしている。それは、デバイスの基礎物理学と産業上の実用性の境界線上に位置しているからである。

結論

高度なDTCO、3次元デバイス構造、および継続的なピッチ縮小が相まって、応力誘起の局所レイアウト効果(LLE)は、二次的な補正事項から、設計およびモデリングにおける中心的な課題へと変貌を遂げました。シリコンにおけるキャリア移動度の機械的応力に対する強い方向依存性に加え、最新のFinFETプロセス集積によって生じる複雑な応力分布により、正確かつ実験的に検証されたLLEモデリングが不可欠となっています。

先進的なCMOS技術において、LLEの特性評価はもはや任意の工程ではありません。これは、ばらつきを考慮したPPA最適化の前提条件となり、従来の「ハッピー・スケーリング」の領域を超えた微細化を実現するための重要な要素となっています。

次は何が待っているのか

次回の記事では、「なぜ」から「どのように」へと話題を移します。すなわち、ストレス、静電効果、ランダムなばらつきを混同させることなく、最新のFinFETプロセスノードにおいて、局所レイアウト効果(LLE)を実験的に分離するにはどうすればよいのでしょうか。そこで、本論文で開発された特性評価手法の核心部分、すなわちテストチップのアーキテクチャ、レイアウトの実験計画法(DOE)、そしてシリコン上で個々のLLEの寄与を分離するために用いられた測定戦略について解説します。